### **NATO UNCLASSIFIED**

# **NATO STANDARD**

# AComP-4691

# MULTI-HOP IP NETWORKING WITH LEGACY UHF RADIOS: MOBILE AD HOC RELAY LINE OF SIGHT NETWORKING (MARLIN)

Edition A Version 1 JUNE 2016

NORTH ATLANTIC TREATY ORGANIZATION

#### ALLIED COMMUNICATIONS PUBLICATION

Published by the NATO STANDARDIZATION OFFICE (NSO)

© NATO/OTAN

**NATO UNCLASSIFIED**

**INTENTIONALLY BLANK**

# NORTH ATLANTIC TREATY ORGANIZATION (NATO) NATO STANDARDIZATION OFFICE (NSO) NATO LETTER OF PROMULGATION

30 June 2016

- 1. The enclosed Allied Communications Publication AComP-4691, Edition A. Version 1, MULTI-HOP IP NETWORKING WITH LEGACY UHF RADIOS: MOBILE AD HOC RELAY LINE OF SIGHT NETWORKING (MARLIN), which has been approved by the nations in the Consultation, Command, and Control Board (C3B), is promulgated herewith. The agreement of nations to use this publication is recorded in **STANAG 4691.**

- 2. AComP-4691, Edition A, Version 1 is effective upon receipt.

- 3. No part of this publication may be reproduced, stored in a retrieval system, used commercially, adapted, or transmitted in any form or by any means, electronic, mechanical, photo-copying, recording or otherwise, without the prior permission of the publisher. With the exception of commercial sales, this does not apply to member or partner nations, or NATO commands and bodies.

- 4. This publication shall be handled in accordance with C-M(2002)60.

Dieter Schmaglowski

Deputy Director NSO Branch Head P&C

Édvardas MAŽEIKIS Major General, LTUAF

Director, NATO Standardization Office

**INTENTIONALLY BLANK**

#### RESERVED FOR NATIONAL LETTER OF PROMULGATION

**INTENTIONALLY BLANK**

## **RECORD OF RESERVATIONS**

| CHAPTER | RECORD OF RESERVATION BY NATIONS |

|---------|----------------------------------|

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

|         |                                  |

Note: The reservations listed on this page include only those that were recorded at time of promulgation and may not be complete. Refer to the NATO Standardization Document Database for the complete list of existing reservations.

**INTENTIONALLY BLANK**

IV

Edition A Version 1

**NATO UNCLASSIFIED**

# **RECORD OF SPECIFIC RESERVATIONS**

| [nation] | [detail of reservation] |

|----------|-------------------------|

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

|          |                         |

Note: The reservations listed on this page include only those that were recorded at time of promulgation and may not be complete. Refer to the NATO Standardization Document Database for the complete list of existing reservations.

**INTENTIONALLY BLANK**

۷I

Edition A Version 1

**NATO UNCLASSIFIED**

#### **TABLE OF CONTENTS**

| Multi-hop IP Networking with Legacy UHF Radios: Mobile Ad hoc Relay Line of sight Networking (MARLIN)                                             | 1-1 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Mobile Ad hoc Relay Line of sight Networking (MARLIN) Profile                                                                                     | A-1 |

| Technical Specifications to Ensure Interoperability of Serial Waveforms for 25 kHz Bandwidth Line of Sight VHF and UHF Radio Data Communications  | B-1 |

| Technical Specifications to Ensure Interoperability of Serial Waveforms for 100 kHz Bandwidth Line of Sight VHF and UHF Radio Data Communications | C-1 |

| Technical Specifications to Ensure Interoperability of Serial Waveforms for 300 kHz Bandwidth Line of Sight VHF and UHF Radio Data Communications | D-1 |

| Technical Specifications to Ensure Interoperability of Serial Waveforms for 500 kHz Bandwidth Line of Sight VHF and UHF Radio Data Communications | E-1 |

**INTENTIONALLY BLANK**

V

VIII Edition A Version 1

**NATO UNCLASSIFIED**

# Multi-hop IP Networking with Legacy UHF Radios: Mobile Ad hoc Relay Line of Sight Networking (MARLIN)

#### Annexes:

- A. MOBILE AD HOC RELAY LINE OF SIGHT NETWORKING (MARLIN) PROFILE

- B. TECHNICAL SPECIFICATIONS TO ENSURE INTEROPERABILITY OF SERIAL WAVEFORMS FOR 25 KHZ BANDWIDTH LINE OF SIGHT VHF AND UHF RADIO DATA COMMUNICATIONS

- C. TECHNICAL SPECIFICATIONS TO ENSURE INTEROPERABILITY OF SERIAL WAVEFORMS FOR 100 KHZ BANDWIDTH LINE OF SIGHT VHF AND UHF RADIO DATA COMMUNICATIONS

- D. TECHNICAL SPECIFICATIONS TO ENSURE INTEROPERABILITY OF SERIAL WAVEFORMS FOR 300 KHZ BANDWIDTH LINE OF SIGHT VHF AND UHF RADIO DATA COMMUNICATIONS

- E. TECHNICAL SPECIFICATIONS TO ENSURE INTEROPERABILITY OF SERIAL WAVEFORMS FOR 500 KHZ BANDWIDTH LINE OF SIGHT VHF AND UHF RADIO DATA COMMUNICATIONS

#### Related Documents:

- a. AC/322(SC/6-AHWG/2)N(2010)0020 Mobile Ad Hoc Relay Line of Sight Networking Concept of Operations

- b. AC/322(SC/6-AHWG/2)N(2010)0021 TCP Performance Enhancement over Wireless Networks: Internet Protocol Traffic Manager (IPTM) proposal

#### AIM

1. The aim of this agreement (MARLIN – Mobile Ad Hoc Relay Line of Sight Networking) is to describe the system concept and set of protocols that provide Internet Protocol (IP) data transfer in multiple-node, multiple-hop dynamic networks employing line of sight (LOS) radio bearers. The protocols were originally developed to provide connectivity amongst ships at sea, but applications with other platforms and in other environments are possible.

#### **AGREEMENT**

2. Participating nations agree to use MARLIN as the interoperability standard for transport of IP data over legacy bearers at UHF, VHF, and HF LOS/Extended LOS (ELOS).

#### **GENERAL**

- 3. The MARLIN system makes use of these legacy bearers by interfacing between an IP data router and a tactical radio. The MARLIN protocol stack provides a number of services:

- Automatic and distributed neighbor discovery and network organization;

- Distributed coordination of transmission to avoid collisions on a shared channel;

- Ad-hoc operation;

- Reliable data delivery with repeat requests and automatic retransmission;

- Dynamic bandwidth allocation in response to reported requirements;

Traffic relay to extend connectivity in multi-hop topologies.

#### IMPLEMENTATION OF THE AGREEMENT

4. This standard is considered implemented by a nation when that nation has placed in service equipment complying with the standards defined in this document.

# ANNEX A MOBILE AD HOC RELAY LINE OF SIGHT NETWORKING (MARLIN) PROFILE

#### A.1. Introduction

#### A.1.1 Overview

The Mobile Ad Hoc Relay Line of Sight Networking (MARLIN) profile describes the system concept and set of protocols that provide Internet Protocol (IP) data transfer in multiple-node, multiple-hop dynamic networks employing line of sight (LOS) radio bearers. The protocols were originally developed to provide connectivity amongst ships at sea, but applications with other platforms and in other environments are possible.

The MARLIN protocol stack provides a number of services:

- Automatic and distributed neighbor discovery and network organization.

- Distributed coordination of transmission to avoid collisions on a shared channel,

- Ad-hoc operation.

- Reliable data delivery with repeat requests and automatic retransmission.

- Dynamic bandwidth allocation in response to reported requirements.

- Traffic relay to extend connectivity in multi-hop topologies.

The protocols are highly parameterized and so are capable of operating over a variety of bearers.

#### A.1.2 Concept of Operations

The primary method of information transfer at sea is through satellite communications (SATCOM). However, SATCOM is not a feasible, all-encompassing solution for operational and tactical IP data networking amongst Coalition ships and other platforms at sea. Not all platforms are fitted for SATCOM, and access is expensive and sometimes limited. In addition, there are vulnerability and survivability issues that necessitate a backup or alternative to SATCOM for communications redundancy.

Several UHF, VHF, and HF LOS/Extended LOS (ELOS) bearers are available as alternatives to SATCOM. Furthermore, nearly all platforms engaged in Coalition operations have access to legacy tactical voice radios in these bands, especially UHF and HF. These legacy bearers could be made available for the transport of IP data.

The MARLIN system makes use of these legacy bearers by interfacing between an IP data router and a tactical radio. Because the radio channel is shared amongst platforms, coordinated channel access is required. Data relay amongst platforms might also be necessary to extend the network beyond line of sight or because radio connectivity is not always all-informed. Furthermore, the system must be highly adaptive to respond to highly dynamic topologies caused by platform mobility and other factors.

A-1

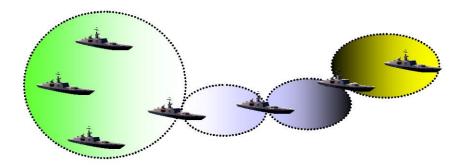

One possible LOS topology is represented in Figure A-1 below. Since the networks are formed in an ad hoc manner and the system is designed to be master-less, the system must self-organize in a distributed manner. This includes the admission of new members to an existing network, and the merging of two or more partitions as they come within range.

Figure A-1: Illustrative MARLIN topology

The expected operational requirements that were considered when designing MARLIN are listed in Appendix A.1. These were derived from current networking requirements; network and platform configurations; and typical battle group sizes, formations, and maneuvers.

#### A.1.3 Protocol Stack and Interfaces

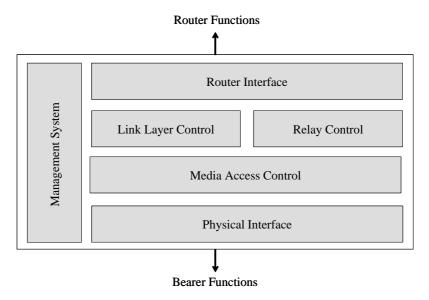

An overview of the MARLIN protocol stack is shown in Figure A-2. MARLIN operates at Layer 2 of the Open System Interconnect (OSI) reference model, between an Internet Protocol (IP) router and a modem, cryptographic device, or radio which is operated in a half-duplex, single-channel mode. The protocol stack is virtual in the sense that any implementation of this standard must execute the functions performed by the sublayers shown. This standard does not mandate a specific framework for software implementation and internal software design within this stack is not subject to interoperability specification. To be compliant, an implementation must comply with all specifications defining message types and message handling on interfaces to bearer and routing functions.

Figure A-2: MARLIN protocol stack

The following are brief descriptions of each component of the protocol stack. Each component is described more fully in subsequent sections:

- Router Interface (RI): communicates with the attached IP router.

- Link Layer Control (LLC): responsible for packet segmentation, reassembly, and duplicate detection. The LLC may also perform data compression and decompression using an open source algorithm.

- Relay Control (RC): monitors the LOS network topology to determine network membership and shortest paths to desired destinations. This helper protocol provides Layer 2 routing when required.

- Media Access Control (MAC): coordinates transmissions on the shared channel using a synchronous Time-Division Media Access (TDMA) scheme, allocating time slots in proportion to reported requirements. In addition, the MAC increases the reliability of data transfer by implementing automatic repeat request (ARQ).

- Physical Interface (PI): connects to the on-air bearer.

#### A.1.4 Example Process Flow

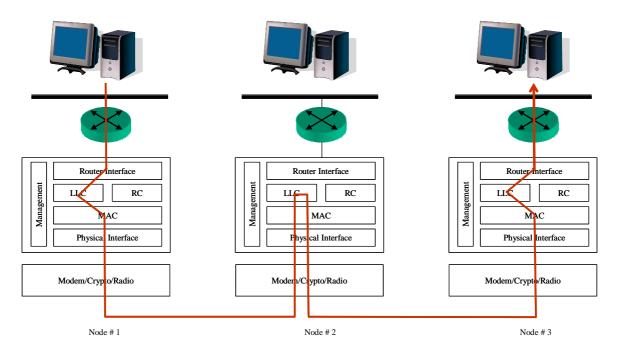

Before describing the operation of the MARLIN protocol layers in detail, it is instructive to consider: the transfer of an IP data packet in a particular scenario. In the following example process flow, one node in a three-node network wishes to transfer data to another node. The nodes are located in a line with the transmitting and receiving nodes at either end of the network as illustrated in Figure A-3. Assuming that the two endpoint nodes are out of each other's LOS, this is the simplest example requiring relay.

Figure A-3: Data transfer in a three-node linear network

An IP packet arriving at the router of the first node destined for the third will be sent as an Ethernet frame to the router interface of the attached MARLIN node. From the Ethernet header information, the router interface at node 1 will recognize the IP payload as a packet to be sent to node 3 and will send the packet to the LLC sublayer where it may be compressed, fragmented, and receive other processing, in preparation for its transmission on the air. The LLC sublayer at node 1, helped by the Relay Control, will know that packets sent to node 3 have to be relayed through node 2 and a MAC Protocol Data Unit (PDU) with next-hop destination #2 will be prepared for transmission with LLC PDU as payload. This MAC PDU will be passed via a synchronous serial physical interface to a modem, crypto, and/or radio, and other radio equipment. Finally, the packet, suitably encapsulated, will be transmitted on the air.

If received successfully at node 2, the de-encapsulated MAC PDU will be passed from the physical interface to the MAC sublayer. The MAC sublayer will pass the PDU payload to its LLC sublayer. The LLC sublayer will recognize from the reported header information that the destination is node 3 and, helped by the Relay Control, will know that node 3 is a direct neighbor. The LLC PDU will be sent to the MAC for relay transmission. A MAC Protocol Data Unit (PDU) with next-hop destination #3 will be prepared for transmission with LLC PDU as payload. From the MAC, the PDU is transmitted on the air through the physical interface.

If received correctly at the physical layer of node 3, the MAC PDU will be passed to the MAC sublayer and the MAC PDU payload, the LLC PDU, will be passed to the LLC sublayer. The LLC at node 3 may have to perform reassembly if the packet was fragmented and decompression if it was compressed, and eventually the original IP packet will be passed to

#### **NATO UNCLASSIFIED**

#### ANNEX A STANAG 4691

the router interface. Finally, the IP packet will be passed on to the router encapsulated in an Ethernet frame.

#### A.1.5 Purpose and Organization of this Document

This document specifies the operation, protocols, and algorithms of the MARLIN system in sufficient detail to ensure implementations of MARLIN complying with this STANAG will be interoperable.

The first Section of this document is this Introduction. The next Sections, in order, describe the Router Interface, Link Layer Control, Relay Control, Media Access Control, Automatic Repeat Request, and Physical Interface in detail. The final section of the main body provides the formats of headers and protocol data units employed in the system. Appendices provide details and supporting information.

#### A.2. Router Interface

#### A.2.1 Overview

IP data inbound to and outbound from the shipboard local area network (LAN) passes through one or more routers. MARLIN provides an alternative link to connect two or more ship networks and so must interface with these IP routers. The connection between each MARLIN node and its attached router is assumed to be a dedicated Ethernet. Furthermore, the Ethernet interface on a MARLIN node must be operated in promiscuous mode as defined in Section A.2.3 .

#### A.2.2 Router Configuration Options and Interaction with MARLIN

Routers connected to MARLIN systems must execute their own IP routing protocol in order to facilitate end-to-end connectivity. Specification of the routing protocol to be employed is beyond the scope of MARLIN specifications, but may for instance consist of Open Shortest Path First (OSPF) using a broadcast-type interface. The (hello) packets used by the router in this case must be presented to the MARLIN system with a multicast address. The system will then translate this to a broadcast address over the MARLIN network, thereby propagating to all reachable routers. The details of the LOS connectivity will be hidden from the router when using such a routing protocol. Alternatively, the IP router may run a mobile ad hoc network (MANET) routing protocol of its own, and only single-hop delivery will be required of the MARLIN nodes. Multi-hop operation is mandated by this standard; single-hop operation is optional.

With regards to OSPF and similar routing protocols, a "proxy" or modified version of the protocol may be helpful to enhance performance. The main reason for this is the need for long routing message intervals. For example, OSPF sends various messages, including OSPF "hello" messages, between routers at specified intervals. The advantage of a short hello interval is that it permits the network to respond quickly to connectivity changes at the router level. However, MARLIN is designed to deal with topology changes at the link-layer, as will be described in Section A.4 below, and for this reason it is beneficial to use a relatively long OSPF hello interval (typically on the order of one minute). A benefit of such an OSPF proxy is that with long hello intervals, the overhead associated with routing on the MARLIN network is quite small. No routing proxy is mandated in this document, but any proxy that is used must be transparent in its operation to allow interoperability with those units which do not have a proxy.

#### A.2.3 IP Addressing, Address Mapping, and Node Identifiers

All discussion in this section applies to both IPv4 and IPv6 addressing; either may be employed, although not simultaneously. The router interfaces attached to a MARLIN subnetwork must all be assigned IP addresses within a contiguous range (e.g. an IPv4 class C subnet). The least significant 8 bits of this IP address (e.g. the host address in an IPv4 class C subnet) is used as the MARLIN Node Identifier (ID). The specification of the MARLIN subnetwork, and the mapping between router interface IP address and MARLIN Node ID are static. These assignments must be configured on each MARLIN node.

A-6

#### **NATO UNCLASSIFIED**

#### ANNEX A STANAG 4691

The Ethernet MAC address on a MARLIN router interface is configured to be 00:*NodeID*:00:00:00:00, where the Node ID is described above. As such, an IP payload in arriving in Ethernet frames with destination field 00:*DestID*:00:00:00:00 will be forwarded to the MARLIN node with a Node ID of *DestID*. Likewise, when a MARLIN node forwards an Ethernet frame to its attached router, it uses 00:*SrcID*:00:00:00:00 in the source field, where *SrcID* is its own 8-bit Node ID.

The Ethernet Address Resolution Protocol (ARP), specified in Request for Comments (RFC) 826, provides a means for resolving IP addresses to Ethernet MAC addresses. Each MARLIN system must proxy responses to ARP requests for the addresses of all nodes within the MARLIN subnet. The proxy functions by intercepting all ARP requests (from the local router) for nodes within the subnetwork and replying with the MARLIN MAC address of the nodes in the network as the MAC address for reaching the node of interest.

All broadcast IP packets should be broadcast on the MARLIN network. IP multicast packets are also broadcast on the MARLIN network. The MARLIN Node ID of 255 is reserved for broadcast.

After stripping the Ethernet header, the IP payload of packets arriving from the router to the router interface are forwarded to the Link Layer Control (LLC) sublayer along with the ID of the egress node, obtained from the Ethernet header as just described. On the destination side, IP packets are forwarded from the LLC sublayer to the router interface, along with the ingress node ID for encapsulation into Ethernet frames and delivery to the router.

#### A.3. Link Layer Control

#### A.3.1 Overview

IP packets arriving from the MARLIN Router Interface have their Ethernet header stripped, are processed, and are queued until needed for transmission. Similarly, PDUs arriving from the MAC sublayer are queued until they are either relayed or reassembled and passed to the Router Interface for delivery to the attached router. The following are the responsibilities of the MARLIN LLC:

- Determine priority for each packet to be transmitted

- Determine need for retransmission/reliable delivery

- Data compression (optional) and decompression (mandatory)

- Fragmentation/reassembly

- Duplicate packet detection.

- Deliver logical protocol data units to MAC

The Link Layer protocol data unit (PDU) header is described in section A.8.6. Along with the source, destination, and relay addresses already mentioned, the header contains several bit fields and flags. These indicate aspects of the LLC responsibilities listed above and described in detail below.

#### A.3.2 Data Priority

The MARLIN LLC determines the priority value of an incoming IP packet from amongst 16 priority values. The priority types and associated values are shown in Table A-1 below. MARLIN management packets are given highest priority, followed by IP routing packets, followed by user data packets, in order of priority. Priority and reliability of user data can be based on any information available in the IP packet and its payload, including protocol type, source and destination IP addresses, and TCP/UDP port numbers.

**Priority Notes** Data Type MARLIN Control Packets 15 Highest priority for network management **IP Routing Control Packets** 13 IP routing information Data PDUs 1-11 User data Not Used 0,12,14 These values are reserved for future use.

**Table A-1: Link Layer Priority**

When data packets of a single priority are considered, packets to be relayed should generally be sent before locally generated user data packets, except that each node may send one locally generated packet for every K relayed packets where K is the number of neighbors that have selected the node as a Multi-Point Relay (MPR), as described in section A.4.4. Remotely

generated traffic is generally preferred to local traffic, as network resources have already been employed in moving the remote traffic at least one hop from source to destination. However, the 1 of K rule just described can be used to prevent local starvation of a relay node when network load exceeds capacity.

#### A.3.3 Compression/Decompression

Data compression is available in MARLIN and, if chosen, is implemented at the LLC sublayer of the transmitting node. Similarly, the LLC of the receiving node executes decompression of the PDU. Data compression is performed using the standard zlib specified in RFC 1950.

#### A.3.4 Packet Fragmentation and Reassembly

The MARLIN LLC also performs fragmentation and reassembly, if required. Fragmentation can occur at the source node as well as all intermediate nodes on the path to the destination node. Reassembly can occur at intermediate and destination nodes. The LLC must be able to reassemble a payload of up to 1500 bytes, the maximum size Ethernet payload.

Note that fragmentation and reassembly can also occur as part of the Automatic Repeat Request (ARQ) mechanism implemented in the Media Access Control (MAC) sublayer, described in section A.6.

#### A.3.5 Duplicate Detection and Time Slot Filling

Since all data packets pass through the LLC sublayer, it also performs duplicate detection. This is especially important for multi-hop relay and broadcast traffic. Duplicates can be detected by monitoring source ID, packet number, and fragment offset. Duplicate packets are dropped when detected.

Finally, the MARLIN LLC sublayer delivers data PDUs consisting of an IP packet payload (complete or fragmented) and a header to the MAC sublayer when needed. The MAC sublayer may request a PDU of a specific length in order to optimally fill its transmission time slot.

#### A.3.6 Queue Reporting

Before each MAC subsystem transmission, the LLC sublayer should calculate the current size of its transmit queues QSize, e.g. in bytes and an estimate of arrival rate, e.g. in bytes/second. QSize should include PDUs that have arrived from the attached router, and those that have been forwarded up from the MAC sublayer and require further relay. Since QSize is used as an indicator of load, the reported value should not include packet fragments awaiting reassembly for which the node is the egress node. The LLC maintains a separate queue for packet reassembly. If ASize is incremented for bytes queued in the transmit queue but is not decremented for bytes dequeued, then the arrival rate between times t<sub>0</sub> and t<sub>1</sub> is given by

#### **NATO UNCLASSIFIED**

#### ANNEX A STANAG 4691

$$\frac{ASize(t_1) - ASize(t_0)}{t_1 - t_0}.$$

An estimate ArrivalRate of the arrival rate can be updated according to

$$\text{ArrivalRate}(t_1) \leftarrow \alpha^{t_1-t_0} \text{ArrivalRate}(t_0) + (1 - \alpha^{t_1-t_0}) \frac{\text{ASize}(t_1) - \text{ASize}(t_0)}{t_1 - t_0} ,$$

where the coefficient  $\alpha$  is chose to satisfy  $\alpha^{M \times T} = 0.5$  for the configured averaging window M  $\times$  T. An averaging window of duration equal to one cycle time, defined in section A.5.3 , shall be used.

#### A.4. Relay Control

#### A.4.1 Overview

For data transfer to two-hop and further nodes, reaching beyond LOS, it is necessary to relay data. To limit the amount of traffic broadcast, and in particular the traffic exchanged to organize the network, the Relay Control sublayer of each MARLIN node selects a subset of its one-hop neighbors via which it can reach all two-hop neighbors (See section A.5.2). These neighbors are called a multi-point relay set, denoted MPR. The concept and nomenclature are borrowed from Optimized Link State Routing (OLSR). The Relay Control sublayer implements functionality similar to OLSR with link state extensions. As the information broadcast by the MPRs is disseminated through the network, nodes can determine the membership of the complete network, find shortest paths to each node, and determine their preferred next-hop relay to every node in the network.

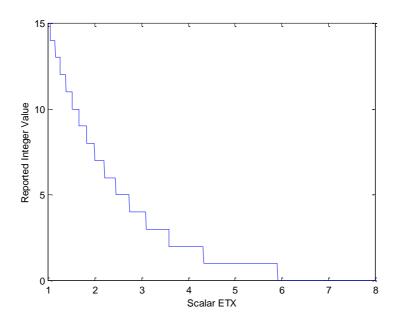

If the link quality LQ denotes the estimate of the probability of successful packet reception for a transmission from one node to a neighbor and the inverse link quality ILQ is the probability of successful packet reception on the return, then the link cost used for the link between the nodes is the symmetric expected transmission count ETX, given by:

$$ETX = \frac{1}{LQ \times ILQ}.$$

This is the expected number of transmissions required to transmit from one node to the other and then receive an acknowledgment in return. The link quality is known to a node based on information obtained by querying the MAC subsystem (see section A.5.9)

#### A.4.2 Relay Control Packet Transmission

The Relay Control (RC) sublayer is responsible for producing RC control packets. This control packet is analogous to the Topology Control packet used by OLSR. The RC PDU contains a list of all the good two-way neighbors of the reporting node, the respective link states of each neighbor, and the respective ETX values for the links to each neighbor. The control packet also includes a sequence number which is incremented by +1 with each transmission. Each node will generate a RC PDU whenever a topology change leads to a change in its two-way neighbor list, and at least once every RC reporting interval T<sub>RI</sub>, usually equal to one cycle time. The RC control packet is passed to the LLC for encapsulation in an LLC header and delivery to the MAC. The RC control PDU is transmitted as a broadcast packet with the reliability flag set to false.

#### A.4.3 Relay Control Packet Processing

RC PDUs generated by other nodes and transmitted by neighbors are received at the MAC and passed to the LLC. Duplicate packets are dropped by the LLC. If the receiving node is

A-11

<sup>&</sup>lt;sup>1</sup> A node i is not required to report a neighbor j if ETX(i, j) + ETX(i, k) > ETX(j, k) for all other neighbors k ≠ j. For in this case, node i is not even a candidate to relay for j, assuming symmetry of ETX. If j can not hear k, then ETX(j, k) = ∞, and j must be reported. If j can hear k, then ETX(j, k) can be estimated from the one-way link quality estimates reported by j and k.

identified as a MPR for the transmitting neighbor, then the LLC PDU will be queued for retransmission. The RC PDU payload is then passed to the RC sublayer. Each successive sequence number replaces the information with the same originator ID, and old packets, determined by monitoring the sequence number, are ignored.

The RC sublayer uses the information contained in the received RC control packets, together if necessary with the one-hop connectivity and link costs obtained from the MAC, to determine full membership in the network. A standard shortest path algorithm can be used to determine the best next-hop to each member of the network. Link costs ETX may be assumed to be symmetric for purposes of this computation. If the RC sublayer does not receive a control packet from an originating node within a suitable RC hold interval  $T_{RH}$ , nominally  $3 \times T_{RI}$ , the data reported by this node is considered out of date, is dropped, and is not used in subsequent shortest path computations. If after removing the information, there is no longer a path to a node, then that node is considered unreachable. When a RC control packet designates a node as a MPR, the originator of that packet is reported as a Multi Point Relay Selector (MPRS) in subsequent packets.

#### A.4.4 Multi-Point Relay Selection Algorithm

Information reported in the RC control packets originating at one-hop neighbors, namely the symmetric ETX link costs, can assist the Multi-Point Relay (MPR) selection executed at each node. Each node shall use a shortest path algorithm with ETX as link cost to determine a preferred next-hop towards each two-hop neighbor. In OLSR with link quality extensions, each good, two-way neighbor that is a preferred next-hop towards at least one two-hop neighbor is selected as an MPR for that node. The same selection criterion is used here. A node selected as an MPR is reported in subsequent RC Control packets accordingly.

#### A.4.5 Data Relay

When a node transmits a broadcast packet, it is heard by all of its one-hop neighbors. Only its RC sublayer MPR neighbors are required to retransmit it, in order to reach two-hop neighbors. This process is then repeated in order to reach nodes even further away. More generally, when a node transmits a broadcast packet, only its RC sublayer MPR neighbors that have not already transmitted it need to retransmit.

#### A.5. Media Access Control

#### A.5.1 Overview

The media access control (MAC) sublayer coordinates transmissions on the shared channel using a synchronous time division media access (TDMA) scheme called Distributed Slot Reservation Media Access (DSRMA). Each MARLIN node maintains a fixed allocation of time slots in each frame, although the specific assignment of slots may change if the topology changes. The remaining slots are allocated to the nodes in a distributed fashion in proportion to their reported demands. Nodes typically acquire additional slots when their demand increases relative to their neighbors and release slots when their demand declines. Certain slots can not be reserved and are set aside for new joiners to enter the network using random access. The MAC layer identifies a subset of its neighbors, called MAC Layer Arbiters (MLA) for mediating slot requests. These need not be the same as the MPR neighbors elected by the RC sublayer, but like MPS the MLAs are required to cover the set of two-hop neighbors. The MAC sublayer also implements an automatic repeat request (ARQ) scheme to facilitate reliable data delivery.

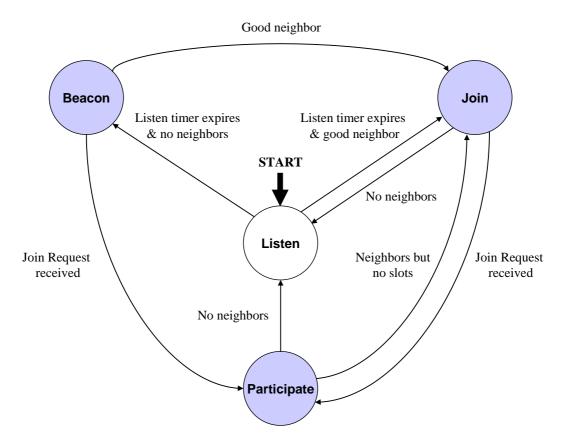

There are four principal states of operation in DSRMA. Existence in one of these states depends on a node's point-in-time in the network, its proximity to and type of neighboring nodes, and its success in reserving TDMA time slots. The state diagram for DSRMA is shown in Figure A-4, and the states are described below.

- **Listen:** in this state, the node listens to gain local information about the network. This state is entered immediately after start-up. A listening node has no transmission slots and no two-way neighbors, but it may have one-way neighbors.

- **Beacon:** a state in which a node has no good one-way or two-way neighbors, but does have a transmission slot, namely a beacon slot in which it will transmit once per frame to announce its presence.

- Join: in this state, a node has at least one good one-way or two-way neighbor, but no persistent time slots reserved for transmission. In this state, a node will periodically use a random access (RA) slot to transmit a join request in which it attempts to reserve a non-RA slot for subsequent transmissions.

- Participate: This is the desired end-state. A node in this state has at least one two-way neighbor and at least one non-RA slot to use for transmission. Once a node has obtained a non-RA slot, it can use it to reserve additional time slots for transmission. Additional use of the contention-based RA slots is not required unless the node loses connectivity with one of its neighbors.

Figure A-4: DSRMA State Diagram

Details of the qualifiers and requirements mentioned in the four states are presented in the following subsections. In particular, the following topics of the MARLIN MAC sublayer will be described in detail:

- Types of neighbors, Multipoint Relays, and Multipoint Relay selectors.

- TDMA timing (cycle and slot structure).

- Slot types and management.

- Subnetwork formation and maintenance.

- PDU types and transmission ordering.

#### A.5.2 Types of Neighbors

DSRMA distinguishes between various types of neighbors. Each node monitors and reports the quality of receptions from all nodes it has recently heard. Based on the link quality assessment, the neighbor is declared a good neighbor, a bad neighbor, or a non-neighbor. The latter is logically equivalent to a node not being reported at all. Good neighbors are further classified as asymmetric (one-way) or symmetric (two-way). If a node assesses its link quality from a neighbor as good, but that node is not reporting the return link as good, the link is asymmetric. If both nodes report the link to the other as good, then the link is symmetric. User data is exchanged only with good, symmetric neighbors. Good, symmetric neighbors are also called one-hop neighbors.

A-14

Two-hop neighbors are nodes that can be reached by relay through a good, symmetric, one-hop neighbor (i.e., a one-hop neighbor of a one-hop neighbor) which are not themselves one-hop neighbors.

With MARLIN, a (possibly empty) subset of one-hop neighbors is selected to distribute MAC control information and mediate slot requests. These neighbors are called MAC Layer Arbiters (MLAs). In an all-informed network where all nodes are direct neighbors no mediation is required and the MLA sets will be empty. More generally, the MLA set must be selected to cover the node's two-hop neighbors. It is desirable that this set be minimal to expedite slot acquisition. One choice for MLA is to re-use the MPR set selected by the RC subsystem, but this is not required. Like MPR selection, this decision can use its own independent criteria to select this set and no specific selection algorithm is mandated. The set of nodes which have selected a given node as a MLA is called the MAC Layer Arbiter Selector set.

In summary, DSRMA distinguishes between the following neighbor types:

- Non-neighbors

- Bad neighbors (interferers)

- Good neighbors:

- o Asymmetric (one-way) neighbors

- Symmetric (two-way) neighbors but not MLAs

- o MLAs

#### A.5.3 TDMA Timing: Cycle and Slot Structure

MARLIN uses a time division multiple access (TDMA) scheme for sharing channel bandwidth on a single frequency amongst the member nodes of a MARLIN network. To achieve synchronization on time slot, cycle, and frame boundaries, each MARLIN node must have access to a source of coordinated universal time (UTC), such as Global Positioning System (GPS).

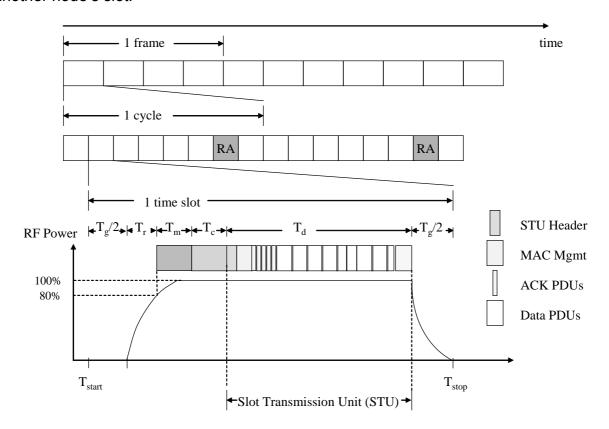

Time on the shared channel is divided into cycles which are further divided into time slots. Each participating node reserves one or more time slots in a cycle for transmission to one or more of the nodes with which it has direct bidirectional connectivity. Slot 0 of cycle 0 begins at midnight January 1, 1970 (Unix time 0 or UTZ). If T is the slot duration in seconds, slot 1 of cycle 0 begins T seconds after UTZ, slot 2 of cycle 0 begins 2T seconds after UTZ, and so on. Slot numbers are recycled after M slots where M is the number of slots in a cycle. The cycle duration is  $M \times T$  seconds. Thus, slot 0 of cycle 1 begins  $T \times M$  seconds after UTZ, slot 1 of cycle 1 begins  $T \times M + T$  seconds after UTZ, and so on. Cycle numbers are recycled after 16 cycles. This is illustrated in Figure A-5.

Setting  $t_z$  to be time in seconds since UTZ, the current slot number, *slot*, and cycle number, *cycle*, are then the given by the integers:

$slot = \lfloor t_z / T \rfloor \mod M$ , and  $cycle = \lfloor t_z / T \times M \rfloor \mod 16$ .

A-15

A new slot begins whenever the division of  $t_z/T$  is an integer value.

Slot timing is defined in terms of the over-the-air transmission and the MARLIN Node Controller is responsible for ensuring that the signal from its transmission does not interfere with reception in another node's slot.

Figure A-5: MARLIN TDMA frame structure

Each time slot is divided into several intervals:

- T<sub>r</sub> time required for a transmitter to ramp up to 80% of its transmit power,

- T<sub>m</sub> time required for modem synchronization,

- T<sub>c</sub> time required for crypto synchronization,

- T<sub>d</sub> time during which data is transmitted, and

- $T_g$  a guard interval equally distributed between the beginning and end of the slot.

The on-air transmission occupies the slot from the time the radio is keyed and begins to ramp up, until the time the radio unkeys. Included in the on-air portion of the slot are modem preambles (used for synchronization), crypto preambles (if required), and portion devoted to data.

Fundamentally, the transmitter must ensure that its on-air transmission does not extend beyond the defined slot boundaries. In systems which support full duplex serial interfaces, it is permissible however to begin sending serial data from the node controller to the crypto or modem prior to the beginning of the slot and to receive data from the crypto or modem after the end of the slot. The unoptimized delay is the sum of two terms. The first is the time from when the first bit is sent from the node controller to the time the signal appears on air. The second is the delay from the time the signal ends until the last bit is received by the node controller. These delay elements can be compensated to optimize transmissions and maximize the duration of the on-air signal while still fitting within the slot when the physical interface is full duplex.

In order to ensure interoperability with networks with heterogeneous equipment, nodes must agree on the maximum total unoptimized delay. This total delay value for the system is the sum of: the worst case (longest) unoptimized transmit delay from any node in the network; the worst case (longest) unoptimized receive delay from any node in the network (and not necessarily the same as the node with the longest transmit delay); and the longest receiver recovery time or radio switching time. Note that the delay values considered are not simply the measured delay values for transmit and receive delay, but rather their values after optimizations have been applied. For illustration, consider a node with a measured transmit delay, from onset of serial data to signal on-air of 50 ms. If that node optimizes its transmission by advancing the time at which it sends serial data by 30 ms, the unoptimized transmit delay is 20 ms. By sharing the worst case value for unoptimized delay, nodes can compute the longest slot that they can transmit and ensure that the most disadvantaged receiver will still be able to successfully receive successive transmissions from the most advantaged transmitter followed by the most disadvantaged transmitter.

During the data portion of the slot, a transmitting node will transmit a slot transmission unit (STU). The STU consists of a STU header followed by a number of MAC protocol data units (PDUs). These MAC PDUs include management PDU types and data PDUs. Protocol data units are added to the STU in priority order, starting with the highest priority 15. Data PDUs awaiting retransmission from the ARQ queue are added before those from the LLC. As described in section A.3.2, remotely generated packets are generally added to the STU before locally generated packets, except that each node is guaranteed a certain fraction of locally generated packets to prevent starvation. PDUs are added until either there is no room left in the STU or there are no more PDUs awaiting transmission. More details on the PDUs being transmitted and their formats are provided in section A.8.

#### A.5.4 Slot Merging

In the event that a node owns two or more consecutive slots, the node may send a single transmission spanning the adjacent slots to minimize overheads. When slots are merged, a single STU is transmitted. Receiving nodes must be able to correctly recognize and decode these merged slots.

#### A.5.5 Types of Slots

There are three types of transmission slots used in MARLIN:

Fixed Allocation

A-17

- Demand Assigned

- Random Access

A MARLIN node will request and release transmission slots in proportion to its own and reported traffic requirements. Thus, bandwidth is dynamically allocated as more or fewer slots are reserved. Each node, however, tries to maintain a minimal number of fixed allocation (FA) slots, typically 1 or 2 per cycle, but always at least 1, regardless of demand. Each cycle also includes 1 or 2 Random Access (RA) slots that can not be reserved and are available for nodes such as new joiners that do not have any reserved slots to request them.

#### A.5.6 Dynamic Bandwidth Allocation

As part of its operation, each node reports its slot demand and obtains the slot demands of its neighbors and its two-hop neighbors. The demand reported by a node is the sum of the LLC transmit queue arrival rate in units half-slot per cycle, the size of the LLC transmit queue in units of half-slots, and the size of the packets scheduled for retransmission by the ARQ mechanism in half-slots, rounded up to the nearest integer. That is, with each transmission node i will report:

Demand(i) = Transmit Arrival Rate + Transmit Queue + Retransmit Queue.

A half-slot is computed as one-half of the product of the slot duration and burst rate,  $0.5 \times T \times R$ .

Each node will obtain these values from its one-hop neighbors j and will also report the sum of demands in its one-hop neighborhood.

$$Target(i) = max \left( Fixed \ Allocation, \frac{(M - M_{RA}) \times Demand(i)}{\displaystyle \max_{j \in N1(i)} \sum_{k \in N1(j)} Demand(k)} \right)$$

Here, M denotes the number of slots per cycle,  $M_{RA}$  denotes the number of RA slots not available for reservation, and N1(j) denotes the set of one-hop neighbors of j together with j itself.

A node whose slot allocation is less than its fixed allocation will always request additional slots if any are available. A node whose slot allocation is less than its fixed allocation may make a priority slot request for an additional slot, described in the next subsection. A node whose slot allocation is less than its target allocation may request additional slots if any are available. If a node has an allocation that is greater than its target allocation, and it can drop slots without reducing its allocation below the number of slots acquired in the last two cycles, then it must identify a slot for release and drop the slot within one cycle time. It is recommended that a node release a slot only as it transmits in it, to allow a full cycle time for another node to acquire

it. No algorithm for deciding which slots to release and which to request when more than one is available is mandated.

The intention of this scheme is that there should be many more slots per cycle than nodes in the network so that each node can acquire its allotment of FA slots and there still be additional DA slots to be exchanged in response to the mechanism just described. In an all-informed network it is a requirement that the number M of slots per cycle be greater than the sum of the number of FA slots for each node and the number of RA slots per cycle.

#### A.5.7 Slot Request and Approval

With each transmission, a MARLIN node transmits its slot ownership table (SOT), a bit-vector indicating the slots it is using for transmission. If a node is a MLA for a neighbor, it will report the SOT of that neighbor as well. Slot ownership tables for interfering nodes, including one-way neighbors, are summarized. In this way, slot ownership and availability is distributed locally. Requests for additional slots are made explicitly. A neighbor signals approval of a slot request made by advertising the slot in the SOT reported for the requesting node. Rejections are implicit when the same slot is advertised for another, competing node. Slot releases are indicated by changing the appropriate bit in the SOT by the transmitter. DSRMA supports two types of slot requests: priority and normal. Priority requests can preempt an existing allocation, whereas normal requests can not.

When a node is first joining a network and has no slots at all reserved, a priority slot request is made. A node with less than its full fixed allotment may also make priority slot requests. These preemptive slot requests must be honored by any other node owning or requesting that slot, unless conflicting priority slot requests are scheduled. In the event of a conflict, nodes approve the lowest node ID for a conflicting priority slot request. When a node makes a priority slot request, all of its neighbors that receive it must respond with an approval or rejection. The requesting node must wait for all its neighbors to have a chance to respond before it may transmit in the slot. Tacit approval is assumed for neighbors (e.g., one-way neighbor) that do not indicate they can hear the requesting node, and at least one explicit approval is required before the requesting node can treat the request as approved.

Ordinary slot requests can be made for any slot which is available when a node's allocation is below its target. The requesting node's MLA neighbors must respond to ordinary requests with approval or rejection, the latter only occurring in the case when a conflict is detected. Note that in an all-informed network, for example, a requesting node has no MLA neighbors and may request a slot and then transmit in that slot without waiting for an acknowledgement. More generally, a node making an ordinary slot request must wait for its MLA neighbors to approve the request before transmitting.

An additional use of the priority slot request is allowed, although not mandated, under this standard. A node which has a persistent one-way neighbor, particularly one in a partition different than its own, may attempt to establish a two-way relationship. To do so, it must transmit in a time slot in which the neighbor is available to receive. As explained more fully in

A-19

the next subsection, such a slot may be determined by transmitting in the RA slot position as determined by the partition id (PID) reported by the one-way neighbor if PID > 0 (a "help merge") or the RA slot in position by the node's own id if the reported PID = 0 (a "help join"). Obtaining such a slot may require the helper node to make a pre-emptive slot request, if it has no alternative. If exercised, this option should be employed sparingly and with suitable back-offs to avoid disrupting the normal operation of the network.

Nodes must monitor the slot ownership tables reported by their neighbors for possible conflicts with slots that have been successfully requested and are being used for transmission. In the event a conflict between the SOT reported by another node and their own is detected, a node must drop any slots reported as owned by other nodes.

#### A.5.8 Network Organization and Maintenance

The self-organization and maintenance of the MARLIN network are addressed in this section. This section describes the steps taken by a node from start-up, how an isolated node joins an organized network, how two organized network (or network partitions) can merge when they come into range, and what happens when they split. It is helpful to refer again to the DSRMA state diagram in figure A-4.

The partition identifier (PID) is used to help organize and identify MARLIN networks and plays an important role in partition joining and merging. In general, the partition identifier is the MARLIN ID of one of the nodes in the partition and when two partitions merge they agree on a common partition identifier. If a single node is not in a network, it will report 0 as a PID to indicate it is a singleton. If a singleton node not in a network hears another node that is in a network transmit it will adopt the partition ID used by the node it hears before transmitting a join request in an appropriate slot. If two distinct partitions come into range, they will adopt the lower partition ID. The partition identifier is updated when a partition splits.

The first DSRMA state that a MARLIN node enters after start-up is the **Listening** state. When first activated, a node must listen for a minimum of one cycle before transmitting. This allows the node to detect existing networks or other nodes.

If neither existing networks nor other nodes are detected, the MARLIN node will enter the **Beaconing** state. While in this state, the node reports a PID of 0 to indicate it is a singleton and can not reach any node other than itself. As defined in appendix 3, the position of the RA slots in the cycle are determined by the PID. When in beacon state, the node should use its own id as a seed to this algorithm and determine the positions of the RA slots accordingly, select a non-RA slot at random, and transmit in that slot. The transmitted beacon consists of a STU header and DSRMA management packet. The node should beacon for two cycles in this non-RA slot. During the second transmission, the node should select a new non-RA slot, drop the first, and announce its ownership of the new slot. It will then transmit for two cycles in the new slot and repeat this operation. The node iteratively beacons for two cycles and chooses another slot, until another MARLIN node or network is discovered. A joining node may announce it can hear the beaconing node and transmit a slot request; if heard, the

A-20

beaconing node should grant the request and transition to participate state. Alternatively, the beaconing node may hear a one-way neighbor and transition to join state.

A node in **Join** state has at least one one-way neighbor and no slots. A joining node will select one of its two-way neighbors if there are any, or else one of its one-way neighbors (if there are more than one), determine a slot in which the target node is available to receive, and schedule a transmission in that slot. A target node should always have at least one slot available in each frame available to receive since the RA slots are reserved for that purpose. If the target is reporting a PID > 0, then an RA slot location can be determined from the PID, as defined in appendix 3. If the target is reporting PID = 0, then the target is itself in either in Join or Beacon state and an RA slot position can be determined by seeding the algorithm in appendix 3 with the target node ID. A joining node will use a PID of 0 to indicate it does not have connectivity to any node other than itself. In its join request, the requesting node should make a priority request to reserve a transmission slot. The requested slot should be a non-RA slot. The node should then listen for at least one cycle time to determine if its join request was successful. Success is achieved when the target node recognizes the requester as a two-way neighbor and the slot request is granted.

If this request is not successful, a random back-off scheme must be employed before attempting another join request transmission since a collision may have occurred with the first request. A specific back-off scheme is not mandated by this profile, however. A node will remain in Join state as long as it has at least one one-way neighbor. If a node in Join state determines it no longer has any one or two-way neighbors it transitions to Listen state.

A node is in **Participate** state if it has at least one two-way neighbor and at least one slot reserved for transmission. Such a node is in an organized network. A node i transitions to Participate state when it hears a neighbor j report it as a good two-way neighbor and identifying a slot reserved for node i's transmissions. When transitioning, node i will set PID(i) = PID(j) unless PID(j) = 0 (i.e., node j is itself in the beacon or the join state). If PID(j) = 0, then node i should set PID(i) = j. In the first case, node i will make a probationary acceptance of its new partition ID, setting a probation timer that will expire after a period  $T_{PID}$ , nominally equal to the Relay Control Hold Time  $T_{RH}$ . If the probation timer expires before a route to the PID is discovered, then node i will elect a new PID as described below.

When in Participate state, a node must engage in partition maintenance. This activity helps to manage the merging and splitting of connected components of the network. First, the activities at node i upon reception from a good, two-way neighbor j are described. If PID(i) = PID(j), there is nothing to do.

- If PID(i) < PID(j) and PID(i) is reachable or probationally so, then node i will not change its PID.

- If PID(i) < PID(j), PID(i) is not reachable and is not on probation, and PID(j) is reachable, then node i will set PID(i) = PID(j) after first setting a blocking timer on its old PID. The blocking timer will expire after a RC hold time T<sub>RH</sub> or if the blocked PID again becomes reachable. When a partition identifier is blocked it is treated as ∞ when compared with another. Setting this blocking timer prevents node i from immediately switching back to

A-21

its old PID should another neighbor report it. Upon expiration of the blocking timer, the blocked value will again become eligible to be a PID.

- If PID(i) < PID(j), PID(i) is not reachable nor on probation, and PID(j) is not reachable, then node i will make a probationary acceptance of PID(j), setting PID(i) = PID(j) after first putting a blocking timer on its old PID to prevent immediately switching back as above. In addition, node i will set a probation timer to expire after a RC hold time period. If the probation timer expires before a route to the new PID is discovered, then node i will elect a new PID, as described below.</p>

- If PID(i) > PID(j) and PID(j) is reachable, then set PID(i) = PID(j).

- If PID(i) > PID(j) > 0 but PID(j) is not reachable, then set PID(i) = PID(j) and set a

probation timer as above.

Each time node i transmits, it checks that PID(i) is still reachable, or if not reachable is on probation. If PID(i) is not reachable and the probation timer has expired, then node i selects the smallest index k from among all nodes that are currently reachable including itself. If k < PID(i), then node i sets PID(i) = k before transmitting. If k > PID(i), then node i will do the same but will also set a blocking timer on the old PID(i) before switching.

When a node changes its partition identifier, it changes the positions of the RA slots in the cycle. If a node has one of the new RA slots reserved for transmission, it should transmit in that slot at the next opportunity. The slot will be dropped but only after a final transmission. If the node has dropped or will be dropping all its slots as a result of the PID change, it should make a priority request for a new non-RA slot at each opportunity. If a node drops all its slots, it should transition to join state.

Even in the absence of a PID change, a node may drop all of its slots due to conflict avoidance. If a node in participate drops all its slots but still has at least one good one-way neighbor, it transitions to Join state. If it finds it no longer has any neighbors, it transitions to Listen state.

#### A.5.9 Link Quality Sensing

Each MARLIN node must maintain a link quality measure LQ (j)  $\in$  [0,1] and an integer link state LS(j)  $\in$  {0, 1, 2, 3} for each neighbor j. The meaning of the states is

| Not heard     |

|---------------|

| Non-neighbor  |

| Bad neighbor  |

| Good neighbor |

|               |

The link quality is an estimate of the probability of successful reception from this neighbor. Before a node j is first heard, LS(j) = 0; When node j is first heard, link quality should be initialized by setting  $LQ(j) = LQ_0$  relatively large and LS(j) = 3. This gives the benefit of the doubt to new joiners. Link quality decision thresholds  $L_{mn}$  for transition from state m to state n are specified. Each time a node j is heard from, the receiving node should update its link

quality estimate. After this, the node must execute the following decision logic to update the link state.

The decision thresholds must satisfy  $0 < L_{21} < L_{12} \le L_{32} < L_{23} < 1$ . The effect of the offset thresholds is to introduce hysteresis into the neighbor decision rule to reduce link state flapping. The initial link quality must satisfy  $LQ_0 > L_{32}$ .

The mechanisms just described are triggered by receptions from neighbors. The case that there are no further receptions must also be addressed. Each time a node j is heard from, an expiration timer for that neighbor is set. If a node is not heard from within 3 cycle times, the link quality and link state are updated by setting  $LQ(j) = LQ_1 < L_{12}$  and LS(j) = 1. If a neighbor expires in this manner, a lost neighbor timer is set for the neighbor equal to 8 cycle times in the future. If the lost neighbor timer expires for a neighbor j, a node should set LS(j) = 0; this will allow it to be treated like a new joiner when it is next heard.

To determine link quality, each node must calculate the proportion of each neighbor's recent transmissions that were successfully received. If a neighbor has been heard from recently and is expected to be heard each time it transmits, then a node can determine a missed slot count MSC by comparing the sequence number in the STU header when received with the last sequence number heard, i.e.

Since 3 bits are used for the STU sequence number, this difference is modulo 8. If there are known conflicts with transmissions (as there could be, for example, with new joiners and one-way neighbors) then the number of missed transmissions may have to be estimated. Given an estimate of missed transmissions, the node should estimate its link quality for this neighbor by setting

$$LQ(j) \leftarrow \beta^{MSC+1} \ LQ(j) + (1 - \beta),$$

where  $\beta$  is a smoothing factor between 0 and 1.

## A.6. MAC Reliability – Hop by hop ARQ

MARLIN implements reliability by means of a hop-by-hop ARQ protocol. If the reliability flag in the MAC Data header is set, the receiving node will acknowledge reception of the packet by sending a MAC Acknowledgement PDU after successfully receiving the PDU. Note that the acknowledgement is only hop by hop and not end-to-end. Reception of the acknowledgment packet indicates that the packet has successfully been transmitted to the next hop but does not guarantee delivery to the final destination. If an ACK packet is received indicating that the first transmission of one or more PDUs requiring reliable delivery was not received successfully, then that PDU should immediately be identified for retransmission and retransmitted at the first available opportunity. If an acknowledgment is not received within 2 cycles of the transmission of a packet with the reliability flag set, the sending node will retransmit the packet. Nodes may choose to retransmit after the intended recipient has had an opportunity to acknowledge reception. Nodes must attempt at least one retransmission of a PDU with the reliability flag set and may choose to drop the PDU after that.

## A.7. Physical Interface

## A.7.1 Crypto/Modem/Radio Interface

This MARLIN node controller standard specifies the timing of the signal transmitted over the air and is specifically designed for TDMA networks. However, this standard does not define the specific characteristics of the signal transmitted over the air. An MARLIN node controller may be embedded within a radio, in which case the interface may be entirely proprietary. In other cases, the MARLIN node controller will be a stand-alone device, connecting to the radio through a cryptographic device and external modem. The vast majority of link cryptographic devices in service require the use of a synchronous serial interface. Hence a synchronous serial interface is defined within this standard. In addition, an ethernet interface is presented as a desirable option.

# A.7.2 Synchronous DCE interface

If the MARLIN Node Controller is not integrated into a radio, the MARLIN Node Controller shall implement a synchronous Data Communications Equipment (DCE) interface that is compatible with EIA-232, EIA-422 or Mil-Std-188-114A.

## A.7.3 Optional Ethernet interface

The modem may provide an Ethernet interface.

#### **A.7.4 Time**

Because the MARLIN TDMA scheme requires precise timing in order to coordinate transmissons on the shared channel, each node must have access to a high precision source of time information. An MARLIN node controller must be able to convert this time source to universal coordinated time (UTC) in order to synchronize its TDMA timing with the other nodes within the network.

To achieve synchronization on time slot and cycle boundaries, the TDMA scheme employed in MARLIN requires an external source of UTC. Examples of precision time sources include Global Positioning System (GPS) or appropriately configured Network Time Protocol (NTP) servers. These time references, if they do not natively provide UTC, can be converted to UTC for use by MARLIN.

In order to be compliant with this specification, the MARLIN Node controller shall be able to determine time to within  $\pm$  10 ms of UTC.

#### A.8. PDU and Header formats

All fields are specified with least significant byte first, least significant bit first.

#### A.8.1 STU Header - Part 1

| Bit Field                    | Number of Bits | Comment           |

|------------------------------|----------------|-------------------|

| Slot Synchronization Pattern | 32             | 0x749713BF        |

| Transmit Node                | 8              | ID of transmitter |

| Partition Identifier         | 8              |                   |

| UTC Flag                     | 1              |                   |

| Sequence Number              | 3              | Bits 1-3          |

| Cycle number                 | 4              | Bits 4-7          |

| Slot number                  | 8              |                   |

| Slot Size                    | 16             | Slot size in ms   |

| CRC                          | 16             |                   |

## **Slot Synchronization Pattern**

The slot synchronization pattern is used for achieving frame synchronization with the data for streaming media. This is considered to be a preamble and is not considered to be part of the STU Header 1 when calculating the CRC.

#### **Transmit Node**

The MARLIN node ID of the STU transmitter

#### **Paritition Identifier**

The partition identifier used by the STU transmitter.

#### **UTC Flag**

Flag to indicate access to precise Universal Coordinated Time. Set to 1 to indicate time accuracy of better than  $\pm 5$  ms.

## **Sequence Number**

The sequence number is incremented with every transmission and is used to assist in determining if the node receiving the transmission has missed transmissions from this node.

## Cycle number

This provides the cycle number of this STU.

#### Slot number

This provides the slot number of this STU.

#### **Slot Size**

The Slot size in ms. Together with other values, this allows a node to join a network without knowing the slot size, number of slots per cycle, or number or number of RA slots per cycle.

A-26

**Edition A Version 1**

#### **CRC**

The 16 bit CRC is computed over the STU Header Part 1, beginning with the Transmit Node field and ending at the end of the Slot Size prior to the CRC. The computation of the CRC is described appendix 2.

#### A.8.2 STU Header – Part 2

| Bit Field     | Number of Bits | Comment                           |

|---------------|----------------|-----------------------------------|

| Spare         | 1              | Set to 1                          |

| Extension bit | 1              | 1 if 64 or more PDUs, 0 otherwise |

| PDU Count     | 6(14)          | 14 Bits if 64 or more packets     |

| Size (PDU 1)  | 12             |                                   |

| Size (PDU 2)  | 12             |                                   |

|               |                |                                   |

| Size(PDU N)   | 12             |                                   |

| Pad           | 0(4)           | Pad to byte boundary if N is odd  |

| CRC           | 16             |                                   |

#### **PDU Count**

The PDU count is the total number of MAC layer PDUs transmitted in this STU. Note that this includes both management and data PDUs with the DSRMA Management PDU counted as PDU number 1. If there are 63 or fewer PDUs, this number is reported using the most significant 6 bits of the first byte. If there are 64 or more PDUs, the extension bit is set to 1 and the PDU count is represented as a 14-bit binary number with the least significant 6 bits taken from bits 2-7 of the first byte of the STU header and the remainder from the second byte. For example, suppose a STU contains 567 PDUs. The binary representation of the decimal 567 is 1 0 0 0 1 1 0 1 1 1 most significant bit first. Writing least significant bit first, the binary representation of the first two bytes in the STU header will then be 1 1 1 1 1 0 1 1 0 0 0 1 0 0 0 0 0.

#### **PDU Size**

This set of fields provides the size of each of the PDUs in the STU in bytes. As long as the STU headers are received correctly, the positions of all MAC PDUs in the slot can be correctly determined. The reported length of each PDU includes all headers and trailers.

#### **CRC**

The 16-bit CRC is computed over the entire STU Header 2, beginning with the PDU Count and ending at the size of the final PDU prior to the CRC. The computation of the CRC is described in appendix 2.

# A.8.3 MAC Management PDU

| Bit Field                        | Number of Bits                        | Comment                                                                      |

|----------------------------------|---------------------------------------|------------------------------------------------------------------------------|

| Туре                             | 4                                     | Set to 2 for MAC Management                                                  |

| Request Flag                     | 1                                     | 1 if slot requests are included, Bit 4                                       |

| Interferer Flag                  | 1                                     | 1 if a summary SOT is provided, Bit 5                                        |

| Number RA slots                  | 2                                     | Bits 6 - 7                                                                   |

| Number Slots                     | 8                                     |                                                                              |

| Number Neighbors                 | 8                                     |                                                                              |

| Demand                           | 8                                     | Transmitting node's demand                                                   |

| Total Demand                     | 8                                     | Demand summed over all one-hop neighbors and transmitting node               |

| SOT/Request Vector               | 8·Ceil(Slots/8) or<br>8·Ceil(Slots/4) | Size depends on whether slot requests are included                           |

| Neighbors                        |                                       |                                                                              |

| Neighbor ID #1                   | 8                                     |                                                                              |

| Neighbor ID #2                   | 8                                     |                                                                              |

|                                  |                                       |                                                                              |

| Neighbor ID #N                   | 8                                     |                                                                              |

| Status for Neighbor #1           | 8                                     | Includes Neighbor type (bits 0-2), reporting flag (Bit 3), and LQ (Bits 4-7) |

| Status for Neighbor #2           | 8                                     |                                                                              |

|                                  | 8                                     |                                                                              |

| Status for Neighbor #N           | 8                                     |                                                                              |

| Neighbor Reporting               |                                       |                                                                              |

| SOT for reported neighbour #1    | 8-Ceil(Slots/8)                       |                                                                              |

|                                  |                                       |                                                                              |

| SOT for reported neighbour #last | 8·Ceil(Slots/8)                       |                                                                              |

| Summary SOT for interferers      | 8·Ceil(Slots/8) or 0                  | Included if interferer flag = 1                                              |

| CRC                              | 16                                    |                                                                              |

#### Type

The Type field is used to distinguish the DSRMA management packet from other MAC layer packets and is set to 2.

A-28

**Edition A Version 1**

## **Request Flag**

The request bit is set to 1 to indicate that this transmission includes slot requests and set to 0 if it does not. This determines whether a SOT or a SOT/Request Vector will be transmitted.

## **Interferer Flag**

This bit is set to 1 if a summary SOT for interferers is provided at the end of the PDU and 0 if none is needed.

#### **Number of RA Slots**

This value reports the number of Random Acess Slots per cycle – 1 in binary. There can be 1, 2, 3, or 4 RA slots per cycle. At least one is required. A value of 0 denotes one RA slot.

#### **Number of Slots**

This reports the total number of slots per cycle – 1 in binary. A maximim of 256 slots per cycle can be supported.

## **Number of Neighbors**

This is the number of neighbors for this node and can be 0.

#### Demand

This is the demand reported by this transmitter as described in section A.5.6.

## **Neighborhood Demand**

This is the sum of the demands reported by all one-hop neighbors plus the transmitting node.

## **SOT/Request Vector**

If the request flag is set to 0, this is a bit vector with entries of 1 indicating slots used for transmission by this MARLIN node. The least significant bit of the first byte of this field corresponds to slot 0, the most significant bit of the first byte corresponds to slot 7, the first bit of the second byte of this field corresponds to slot 8 and so on. The field will be padded out to the byte boundary with zeros.

If the request flag is set to 1, then this vector includes slot request information as well as slot ownership information. The two least significant bits of the first byte of this field then correspond to slot 0, with values interpreted as:

0 = not owned and not requested.

1 = owned, i.e., reserved for transmission

2 = ordinary slot request,

3 = priority slot request.

The most significant two bits of the first byte correspond to slot 3, the first two bits of the second byte correspond to slot 4, and so on. The bit vector is padded to the byte boundary with zeros.

#### **Neighbor Identifiers**

This indicates the IDs of the neighbors this node hears. The number of neighbors has been reported earlier in the PDU.

## **Neighbor Status**

A-29

**Edition A Version 1**

One byte is reported for each neighbor. Neighbors are reported in order in which the IDs appear in the list immediately preceding it. The first 3 bits, bits 0 - 2 are used to indicate neighbor status as described in section A.5.2. The values employed are:

- 0 = Non-neighbor

- 1 = Bad neighbor

- 2 = Asymmetric (one-way) neighbor

- 3 = Symmetric (good, two-way) neighbor but not MLA

- 4 = MAC Layer Arbiter (MLA)

The next bit, bit 3, is used to indicate whether further reporting for this node will occur, i.e., this neighbor's demand value and SOT table. In normal operation when no priority requests are present, a node will report these entries for all neighbors in its MLA Selector set.

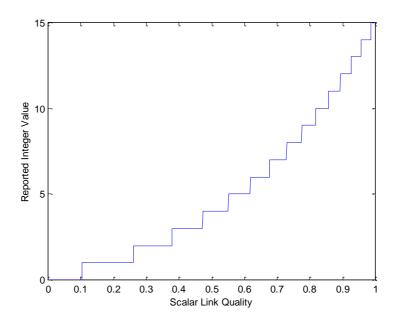

The final bits, bits 4-7 are used to report link quality (LQ) received from this neighbor. The Link Quality, as described earlier. Link Quality is a scalar between 0 and 1 (representing the probability of successful packet reception) and must be reported as 4-bit integer between 0 and 15. To give more granularity to the higher probabilities and therefore the region of interest, a non-linear mapping is employed, with the integer value reported being given by  $2 \cdot (17/2)^{LQ} - 2$ , rounded to the nearest integer. The result of this operation is illustrated in the figure below.

| Value | LQ             | Value | LQ             | Value | LQ             | Value | LQ             |

|-------|----------------|-------|----------------|-------|----------------|-------|----------------|

| 15    | (0.986, 1.0]   | 11    | (0.856, 0.892] | 7     | (0.676, 0.728] | 3     | (0.379, 0.473] |

| 14    | (0.957, 0.986] | 10    | (0.817, 0.856] | 6     | (0.618, 0.676] | 2     | (0.261, 0.379] |

| 13 | (0.926, 0.957] | 9 | (0.775, 0.817] | 5 | (0.551, 0.618] | 1 | (0.104, 0.261] |

|----|----------------|---|----------------|---|----------------|---|----------------|

| 12 | (0.892, 0.926] | 8 | (0.728, 0.775] | 4 | (0.473, 0.551] | 0 | [0.0, 0.104]   |

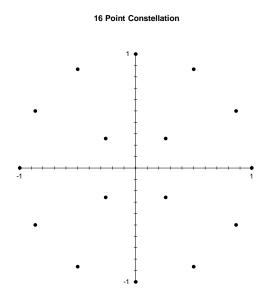

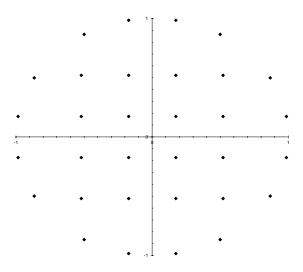

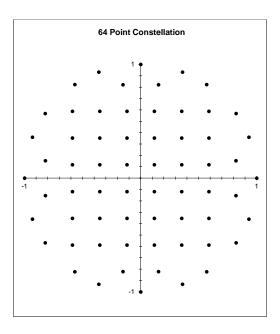

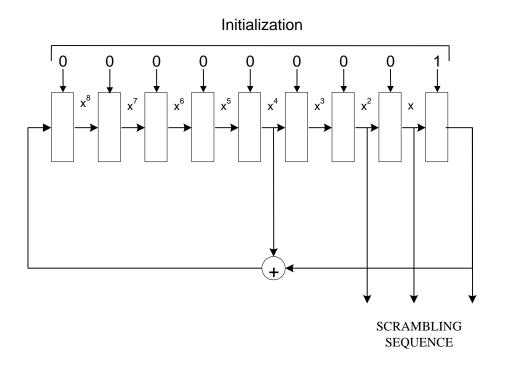

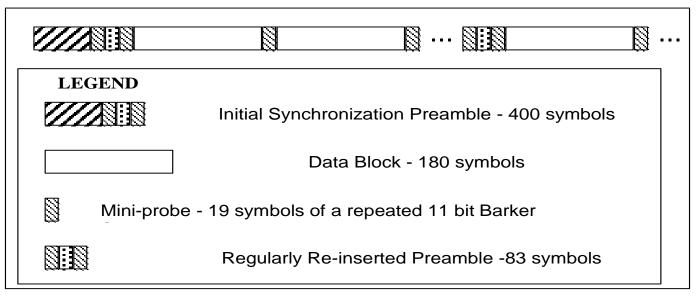

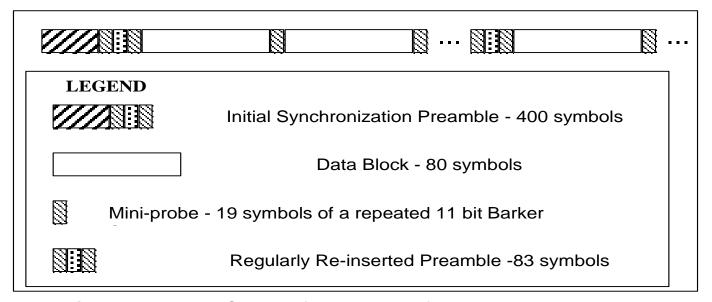

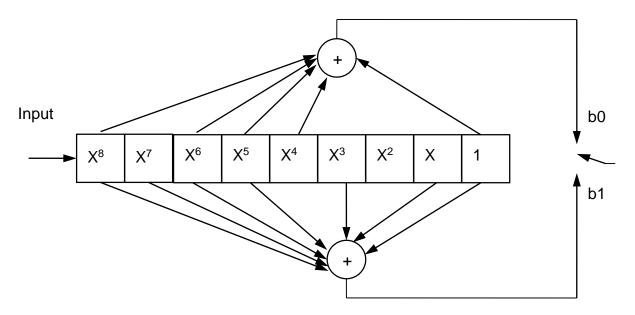

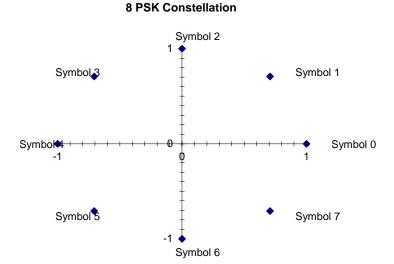

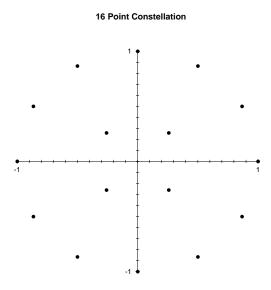

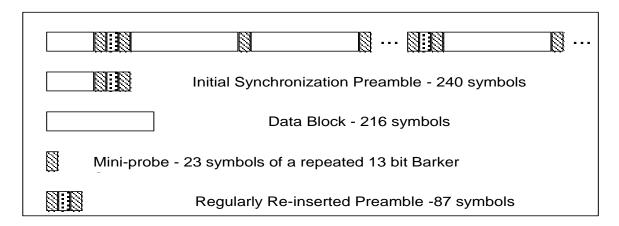

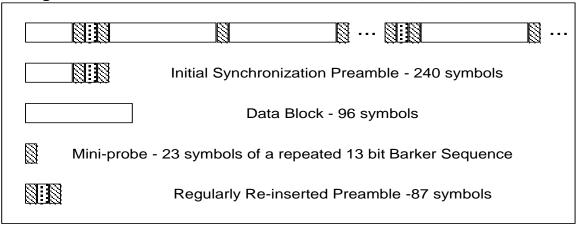

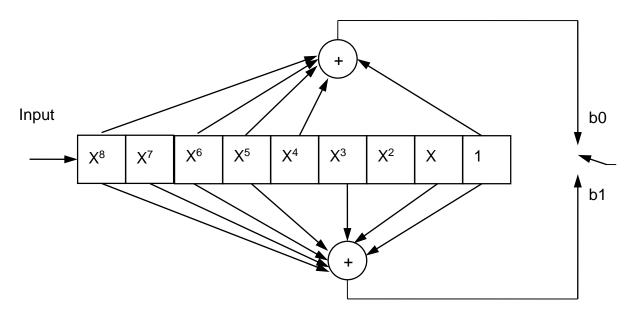

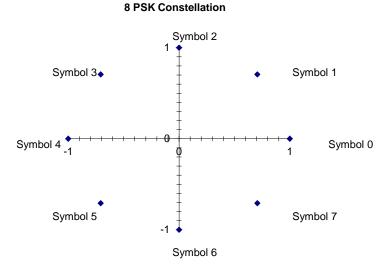

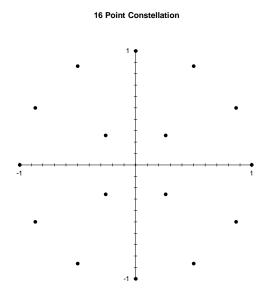

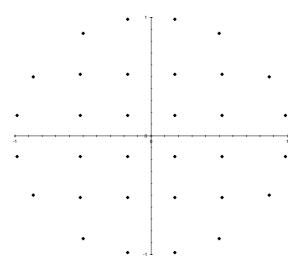

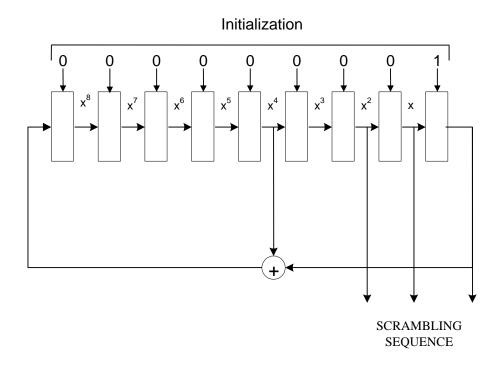

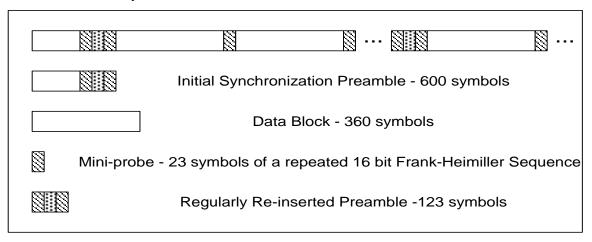

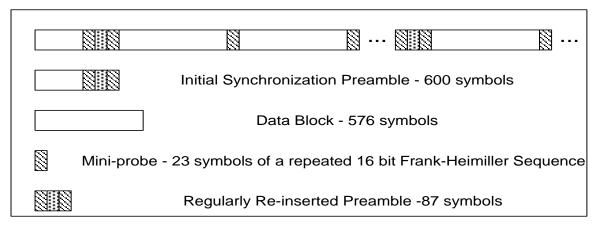

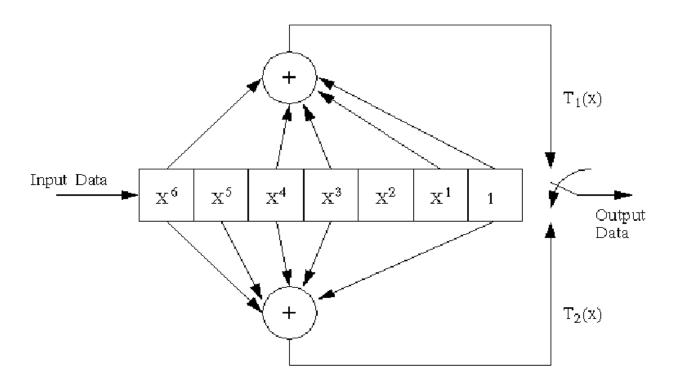

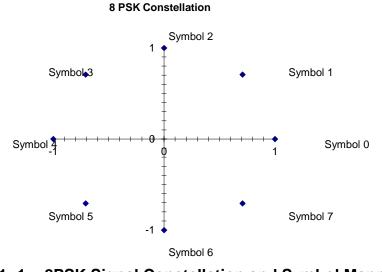

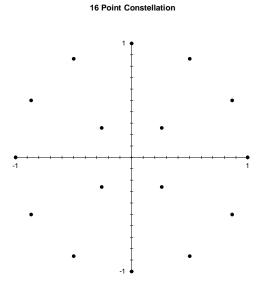

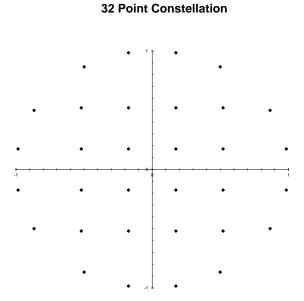

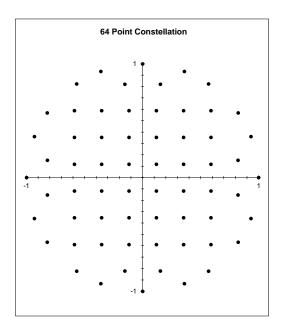

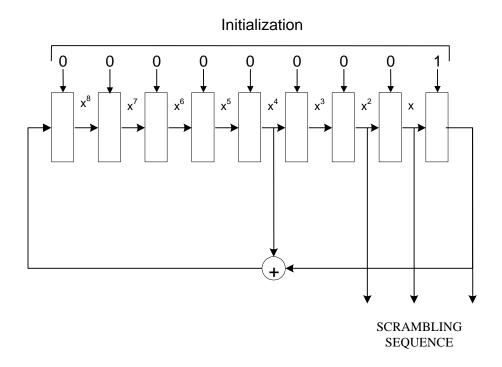

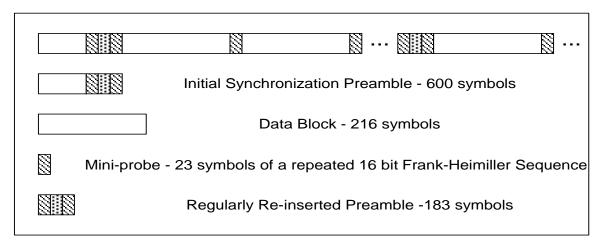

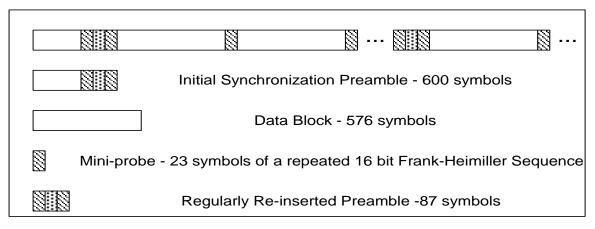

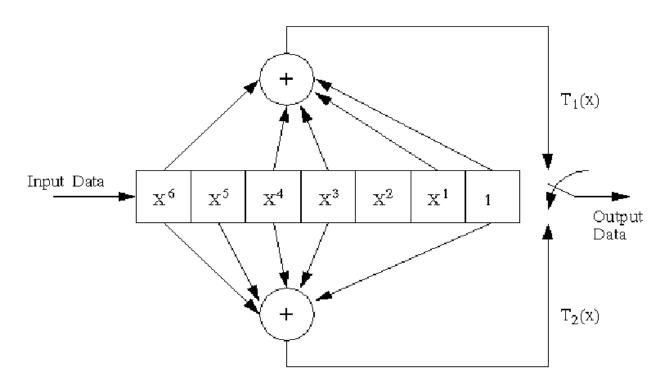

## **SOT for Reported Neighbors**