AEP-41 Volume 1 (Edition 1)

ALLIED ENGINEERING PUBLICATION

# **AEP 41**

# UNIFIED ELECTROMAGNETIC ENVIRONMENTAL EFFECTS (UE³) PROTECTION, PHILOSOPHY AND METHODOLOGY

Volume 1

February 2004

AEP-41 Volume 1 Edition 1

AEP-41 Volume 1 (Edition 1)

**BLANK PAGE**

AEP-41 Volume 1 (Edition 1)

# NORTH ATLANTIC TREATY ORGANISATION NATO STANDARDIZATION AGENCY NATO LETTER OF PROMULGATION

February 2004

- 1. AEP-41, Volume 1 (Edition 1) UNIFIED ELECTROMAGNETIC ENVIRONMENTAL EFFECTS (UE³) PROTECTION, PHILOSOPHY AND METHODOLOGY is a NATO/PFP UNCLASSIFIED publication. The agreement of nations to use this publication is recorded in STANAG 4567.

- 2. AEP-41, Volume 1 (Edition 1) is effective upon receipt.

Brigadier General, PLAR Director NSA

AEP-41 Volume 1 (Edition 1)

**BLANK PAGE**

AEP-41 Volume 1 (Edition 1)

## **NATIONAL RESERVATIONS**

| Nation | Specific Reservations |

|--------|-----------------------|

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

|        |                       |

AEP-41, Volume 1 (Edition 1)

AEP-41 Volume 1 (Edition 1)

**BLANK PAGE**

AEP-41 Volume 1 (Edition 1)

### **AMENDMENTS**

| No. | Reference/Date of amendment | Date entered | Signature |

|-----|-----------------------------|--------------|-----------|

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

|     |                             |              |           |

AEP-41, Volume 1 (Edition 1)

AEP-41 Volume 1 (Edition 1)

**BLANK PAGE**

AEP-41 Volume 1 (Edition 1)

#### **TABLE OF CONTENTS**

#### 1.0 TABLE OF CONTENTS

#### 2.0 AEP 41, EXECUTIVE SUMMARY

#### 2.1 INTRODUCTION TO AEP 41

- 2.1.1 Balanced E<sup>3</sup> Protection

- 2.1.2 E<sup>3</sup> Protection Needs

- 2.1.3 Methodology

#### 2.2 SCOPE FOR AEP 41

- 2.2.1 Volume I

- 2.2.2 Volume II

- 2.2.3 Volume III

- 2.2.4 Volume IV

- 2.2.5 Volume V

- 2.2.6 Volume VI

- 2.2.7 Volume VII

#### 2.3 REQUIREMENTS

#### 3.0 AEP 41, VOLUME I, EXECUTIVE SUMARY

#### 3.1 INTRODUCTION

- 3.1.1 Philosophy

- 3.1.2 Methodology

#### 3.2 SCOPE FOR AEP 41, VOLUME I

- 3.2.1 Philosophy and Methodology

- 3.2.2 Risks

#### 4.0 UNIFIED ELECTROMAGNETIC ENVIRONMENTAL EFFECTS PROTECTION

#### 4.1 OVERVIEW

- 4.1.1 General

- 4.1.2 Electromagnetic Environments (EMEs)

- 4.1.3 Electromagnetic Environmental Effects (E3) Survivability

- 4.1.3.1 UE<sup>3</sup> Protection

- 4.1.3.2 Alternate and Special Protection Methods

- 4.1.3.2.1 Alternate Methods

- 4.1.3.2.2 Special Protection Methods

AEP-41 Volume 1 (Edition 1)

- 4.1.4 Evolution of Electronics and Increased COTS/NDI Usage

- 4.1.5 Unified E<sup>3</sup> Protection Approach Overview

- 4.1.5.1 General

- 4.1.5.2 Route to Adequate Protection

- 4.1.5.2.1 Development of E<sup>3</sup> Protection

- 4.1.5.2.2 Hardening Requirement

- 4.1.5.2.3 Testing and Validation of UE<sup>3</sup> Protection

- 4.1.5.2.4 Stress Transfer Function

# 4.2 LIFE-CYCLE APPLICATION OF THE $\mbox{UE}^3$ PROTECTION PHILOSOPHY AND METHODOLOGY

- 4.2.1 General

- 4.2.2 Phase 1: Concept Definition

- 4.2.2.1 General

- 4.2.2.2 Requirements

- 4.2.2.3 Unified E<sup>3</sup> Protection Concept

- 4.2.2.3.1 General

- 4.2.2.3.2 EM Barrier Protection Concept

- 4.2.2.4 Life-Cycle Program

- 4.2.3 Phase 2: Engineering Development

- 4.2.3.1 General

- 4.2.3.2 E<sup>3</sup> Allocation Process Overview

- 4.2.3.3 Unified E<sup>3</sup> Protection Allocation

- 4.2.3.3.1 Performance Requirements

- 4.2.3.3.2 Allocation Process

- a. MSCEs Immunity

- b. Margin

- c. Internal Residuals

- d. External EME Stress

- e. Barrier Performance Requirements

- 4.2.3.4 Design for a Linear Application

- 4.2.3.4.1 Unified Barrier Performance Requirements (Single EME & Immunity)

- a. General Approach

- 1) EME/Immunity

- 2) Margin

- 3) Residual and Performance Requirements

- b. Enclosure Port Performance Requirements

- c. Penetration Port Performance Requirements

- 1) Penetration Port

- 2) Immunity Equivalent Source

- 3) Penetration Equivalent Source

- 4) Performance Requirements

- 4.2.3.4.2 Unified Barrier Performance Requirements

(Single EME and Multiple Immunities)

a. Specific Performance Requirements (One MSCE)

#### **NATO/PFP UNCLASSIFIED**

AEP-41 Volume 1 (Edition 1)

- b. Specific Performance Requirements (Multiple MSCEs)

- 4.2.3.4.3 Unified Barrier Performance Requirements (Multiple EMEs and Immunities)

- a. General

- b. Unified Performance Requirements for Ports

- c. Unified Performance Requirements for EMEs

- 4.2.3.4.4. Allocations for Internally Generated EMEs

- 4.2.3.4.5. Design for Non-Linear Application

- 4.2.3.5 Testing

- 4.2.3.5.1 Tests

- 4.2.3.5.2 Unification of Tests

- 4.2.3.6 Life-Cycle Database

- 4.2.4 Phase 3: Production

- 4.3.4.1 General

- 4.3.4.2 Quality Assurance and Control

- 4.3.4.3 Testing

- 4.3.4.4 Life-Cycle Database

- 4.2.5 Phase 4: Deployment

- 4.2.5.1 General

- 4.2.5.2 Traditional Factors

- 4.2.5.3 Modern Factors

- 4.2.5.3.1 General

- 4.2.5.3.2 Operational Status

- a. DMSMS

- b. Improved Capabilities

- c. COTS/NDIs

- d. Modernization Through Spares

- 4.2.5.3.3 Technology

- 4.2.5.4.Life-Cycle Database

- 4.2.6 Surveillance Test (ST)

- 4.2.6.1 Hardness Assurance

- 4.2.6.2 Sustainment Assurance

- 4.2.6.3 Life-cycle Database

- 5.0 SUMMARY

- 6.0 CONCLUSIONS

- 7.0 APPENDIX

- 7.1 REFERENCES

- 7.2 ACRONYMS

- 7.3 DEFINITION

AEP-41 Volume 1 (Edition 1)

**BLANK PAGE**

AEP-41 Volume 1 (Edition 1)

#### **AEP 41, VOLUME I**

# UNIFIED ELECTROMAGNETIC ENVIRONMENTAL EFFECTS (UE<sup>3</sup>) PROTECTION, PHILOSOPHY AND METHODOLOGY

#### 2.0 AEP-41, Executive Summary

There is a general consensus for an unified approach to the protection and hardening of all NATO military platforms, systems and equipments (hardware) against Electromagnetic Environmental Effects (E<sup>3</sup>) caused by the plethora of Electromagnetic Environments (EMEs) that these platforms, systems and equipments are subjected to during their deployment life. These E<sup>3</sup> can adversely impact the operational capability of this military hardware resulting in their inability to accomplish their mission or even putting the crew's safety at risk. The EMEs are generated by natural, operational and Additionally, today's complex military operational environment is hostile sources. characterized by: multi-national operations, increasingly crowded EM spectrum coupled with a reduction of bandwidth allocated for exclusive military use, military hardware whose mission performance is dependent on electronics, and hardware that is increasingly dependent on more energy sensitive Non-Developmental Items (NDIs) and Commercial-Off-The-Shelf (COTS) electronic components. Traditional hardening against the total battlespace EMEs has been accomplished by considering each EME individually and serially. The Conference of National Armaments Directors (CNAD) recognized the need for a Unified E3 (UE3) protection policy, and directed the development of an Allied Engineering Publication (AEP) 41 and an associated Standardization Agreement (STANAG) 4567 to describe and define this policy. The proposed UE<sup>3</sup> protection approach can be applied to all six Operational Categories (OCs) of NATO military hardware. These six OCs are:

- OC1 Land Mobile Systems

- OC2 Static Land Systems

- OC3 Space Systems

- OC4 Sea Platforms

- OC5 Air Platforms

- OC6 Command, Control and Information Systems

The CNAD approved the following seven AEP 41 volumes to detail the different functional areas required to achieve, produce and sustain affordable UE<sup>3</sup> protection and survivability:

- a) Volume I, Unified Electromagnetic Environmental Effects (UE<sup>3</sup>) Protection, Philosophy and Methodology

- b) Volume II, Electromagnetic (EM) Environments (EMEs), E<sup>3</sup>, and Operational Categories

- c) Volume III, Electromagnetic Coupling

- d) Volume IV, Susceptibility of Platforms, Systems and Equipment to E<sup>3</sup>

AEP-41 Volume 1 (Edition 1)

- e) Volume V, Unified Hardening and Protection Against E<sup>3</sup>

- f) Volume VI, Testing and Validation of E<sup>3</sup> Protection

- g) Volume VII, Hardness and Sustainment Assurance, and Surveillance Test

The basic philosophy is to provide a User-controlled, performance-based approach to developing cost effective, verifiable, producible, maintainable and sustainable UE<sup>3</sup> protection for NATO military hardware. The methodology for implementing UE<sup>3</sup> protection to all types of military hardware is based on use of an EM barrier protection concept that is applicable to linear cases. In addition, this methodology is inherently accommodating and flexible for future growth and changes, and for sustaining EM hardness against degradations resulting from usage, age, maintenance and repairs, changes and additions, and ambient environments. This AEP uses extensively the UE<sup>3</sup> Protection Philosophy and Methodology documented in QSTAG 1051.

#### 2.1 INTRODUCTION FOR AEP 41

- **2.1.1 Balanced E<sup>3</sup> Protection**. This AEP describes an approach for achieving adequate, affordable and balanced UE<sup>3</sup> protection and survivability in the battlespace for all classes of NATO military platforms, systems, and equipments (all three defined as hardware) of the six operational categories. Balance is achieved between several factors. First, the protection design is balanced for unified coverage of the EME stresses encountered during hardware operations. Second, a balance is achieved between the protection provided and hardware cost and operational impact. Third, the User can balance the level of protection against risk of operational degradation in the presence battlespace EMEs. The philosophy embodied in AEP 41 does not mandate design solutions; but instead, provides a performance-based methodology that allows the User the flexibility for deriving the final UE<sup>3</sup> protection design to meet performance requirements.

- **2.1.2** E<sup>3</sup> Protection Needs. Adequate E<sup>3</sup> protection of electronic/electrical military hardware is essential since such hardware must operate during and after exposure to increasingly severe, complex and changing EMEs that can potentially impact crew safety as well as degrade or even destroy mission essential performance Potential battlespace EMEs are listed in Table 1. Meeting the E<sup>3</sup> protection requirement has become more difficult due to the post-cold war policy of deploying NATO coalition forces (even combined with UN forces) consisting of military hardware hardened to different E<sup>3</sup> levels into many different areas each with its own set of EME threats. This disparity in E<sup>3</sup> hardening, combined with different national policies on E<sup>3</sup> survivability sustainment, has resulted in deployment of NATO hardware with widely varying E<sup>3</sup> survivability/vulnerability levels. Thus, the deployed force has EM compatibility (EMC) problems. In addition, most of the hardware was developed in the cold war. Post-cold war policy of most NATO countries is to extent the operational life of their deployed hardware by a factor of two or more. This lifetime extension combined with rapidly advancing technology and increasing obsolescence has become the reason for multiple modernization cycles (was one, now eight-to-ten) and the increasing use of COTS/NDIs and advanced technologies both of which tend to have lower energy upset and damage thresholds. These new impacting factors are in addition to the traditional ones (worsen by the longer deployment lifespan) that can degrade E<sup>3</sup> survivability such

AEP-41 Volume 1 (Edition 1)

as ambient environments, corrosion, aging, usage, and repeated maintenance and repairs. Thus, the combination of these new and old factors has greatly increased the difficulty of sustaining E<sup>3</sup> survivable hardware.

**Table 1. Characteristics of Battlespace EMEs**

| Externally Generated Electromagnetic Environments     |                         |                                                                       |                        |

|-------------------------------------------------------|-------------------------|-----------------------------------------------------------------------|------------------------|

| Environment                                           | Туре                    | Waveform                                                              | Propagation *          |

| Near Strike Lightning (NSL)                           | Natural                 | Pulse                                                                 | Radiated and Conducted |

| Direct Strike Lightning (DSL)                         | Natural                 | Pulse                                                                 | Conducted              |

| High Altitude Electromagnetic Pulse (HEMP) E1, E2, E3 | Hostile                 | Pulse                                                                 | Radiated and Conducted |

| Source Region EMP (SREMP)                             | Hostile                 | Pulse                                                                 | Radiated and Conducted |

| Non-Nuclear EMP<br>(N <sup>2</sup> EMP)               | Hostile                 | Pulse                                                                 | Radiated               |

| Electromagnetic<br>Emissions                          | Electronic Operation    | Pulse, CW and<br>Modulated CW                                         | Radiated and Conducted |

| High Intensity Radiated Field (HIRF)                  | Electronic<br>Operation | CW Pulsed, CW and<br>Modulated CW                                     | Radiated               |

| Electronic Counter<br>Measures (ECM)                  | Hostile                 | CW and Modulated CW                                                   | Radiated               |

| High Power Microwave (HPM)                            | Hostile                 | CW Pulsed, CW and<br>Modulated CW, single or<br>multiple Bursts of CW | Radiated               |

| Ultra-Wideband (UWB)                                  | Hostile                 | Pulse, single or multiple                                             | Radiated and Conducted |

| Precipitation- Static (P-Static)                      | Natural                 | Pulse                                                                 | Conducted              |

| Electrostatic Discharge (ESD)                         | Natural                 | Pulse                                                                 | Radiated and Conducted |

| System Generated EMP (SGEMP) External                 | Hostile                 | Pulse                                                                 | Radiated and Conducted |

| Dispersed EMP (DEMP)                                  | Hostile                 | Pulse                                                                 | Radiated and Conducted |

<sup>\*</sup>Propagation is the method by which energy arrives to the victim from the source

| Internally Generated Electromagnetic Environments |                         |                            |                        |

|---------------------------------------------------|-------------------------|----------------------------|------------------------|

| Enviroment                                        | Type                    | Waveform                   | Propagation *          |

| Electromagnetic<br>Emissions                      | Electronic<br>Operation | Pulse, CW and Modulated CW | Radiated and Conducted |

AEP-41 Volume 1 (Edition 1)

| Electrostatic Discharge (ESD)    | Natural | Pulse | Radiated and Conducted |

|----------------------------------|---------|-------|------------------------|

| SGEMP - Internal (Box and Cable) | Hostile | Pulse | Radiated and Conducted |

<sup>\*</sup>Propagation is the method by which energy arrives to the victim from the source

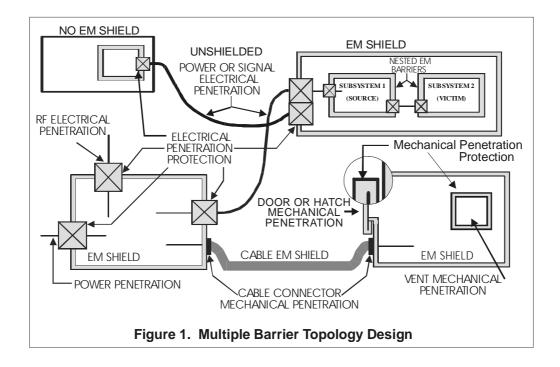

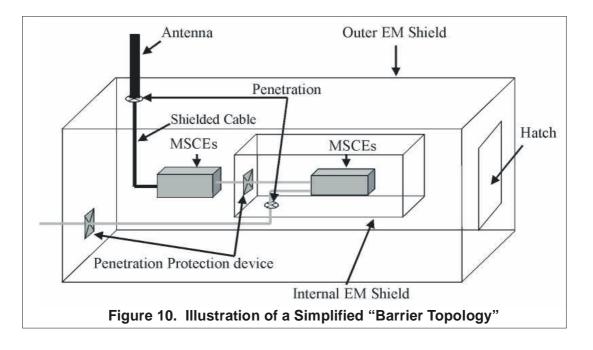

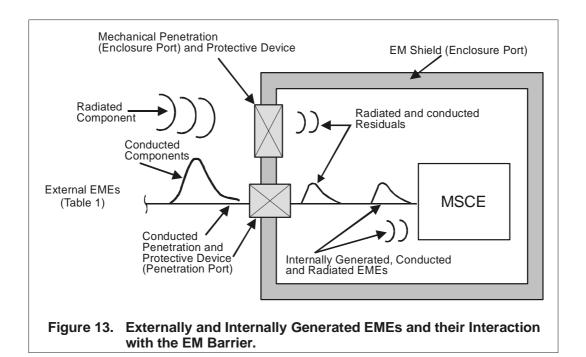

**2.1.3. Methodology.** The method of achieving UE<sup>3</sup> protection and survivability is through the use of EM barrier(s) plus special protective measures to protect Mission and Safety Critical Electronics (MSCEs). An EM protection barrier consists of two elements: one or more EM shields, and the necessary electrical and mechanical penetrations through the shield(s). To maintain the barrier effectiveness, penetration protection devices must be provided for all penetrations in the EM shield. Figure 1 illustrates the EM barrier protection concept applied to a multi-element system. (Note that this concept can be effectively applied to military hardware that has effectively no shield e.g., modern aircraft (OC5).) This protection concept is familiar to digital, circuit, integration and system designers; and, does not require the development of new design practices. The

AEP-41 Volume 1 (Edition 1)

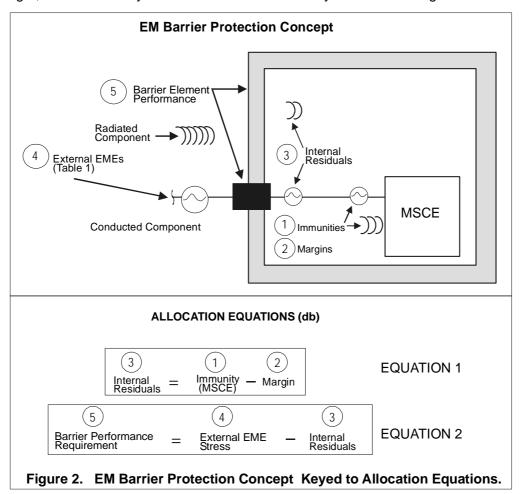

illustrated example employs multiple closed metallic EM barrier topologies to reduce the externally and internally generated EME stresses (conducted and radiated) to residual stress levels consistent with acceptable operation of the protected MSCEs. Choosing the acceptable operational levels and, in turn, the EM barrier performance requirements involves a process of balancing the externally and internally generated EME stresses, the MSCEs immunities, and the margin selected to control risk. The engineering trade studies necessary to achieve this balance are through the allocation process, illustrated in Fig 2, which is usually iterative and serves basically as a risk management tool. If the

EM barrier concept is properly designed and implemented into military hardware, UE<sup>3</sup> protection and survivability can be achieved that is affordable and producible as well as verifiable, maintainable and sustainable throughout the hardware's operational life. Additionally, an integral and essential part of this methodology is testing, which is conducted throughout all four of the acquisition life-cycle phases to insure that the EM protection design is: adequate and complete during concept and engineering development, properly implemented during production, and properly maintained and

AEP-41 Volume 1 (Edition 1)

sustained during deployment. Furthermore, the EM barrier protection concept facilitates unified testing by focusing on the barrier rather than individual E³. Since this methodology can create benign internal EME stresses to which the MSCEs must survive, the EM barrier facilitates Diminishing Manufacturing Sources and Material Shortages (DMSMS) and technology insertions, especially COTS/NDIs, and upgrades/enhancements.

#### 2.2 SCOPE FOR AEP-41

The general scope of this AEP is to document how affordable for all UE<sup>3</sup> survivability can be achieved, verified, produced and sustained for all six categories of NATO hardware using the EM barrier protection concept. This scope of work will be accomplished in the following seven volumes.

- **2.2.1. Volume I.** This volume provides the philosophy and methodology for achieving affordable UE<sup>3</sup> protection and survivability through the use of the EM barrier protection concept. A discussion of how to apply the EM barrier protection methodology to achieve UE<sup>3</sup> survivability that is affordable, verifiable, producible and sustainable in todays and the future battlespace is provided.

- **2.2.2. Volume II.** This volume provides the typical requirements for and defines and discusses the potential battlespace EMEs listed in Table 1 that military hardware must be protected against in order to be E³ survivable in the battlespace. These EMEs interact with military hardware causing E³, which are defined and discussed. Furthermore, military hardware (platforms, systems and equipments) of the six operational categories are discussed.

- **2.2.3. Volume III.** This volume provides detailed discussion of E<sup>3</sup> coupling for the various classes of military platforms, systems and equipments defined in Vol. II. Understanding E<sup>3</sup> coupling is critical because the EM barrier is basically an E<sup>3</sup> management tool to insure that the resultant residual levels from the EME generated stresses are lower than the MSCE immunity levels by a realistic margin. (Margin depends on mission criticality of hardware and permissible risk; therefore, margin is usually 15-20 dB, which is adequate only if combined with a thorough life-cycle program.)

- **2.2.4.** Volume IV. This volume discusses E³ susceptibilities common to the six categories of NATO military hardware defined in Vol. II. How these E³ susceptibilities occur, what they are, and how they affect these various hardware classes in the battlespace is discussed.

- **2.2.5. Volume V.** This volume describes how to apply the EM barrier protection concept to achieve UE<sup>3</sup> protection and survivability against the E<sup>3</sup> susceptibilities described in Vol. IV resulting from the E<sup>3</sup> coupling described in Vol. III for the six operational categories of NATO hardware defined in Vol. II. Volume V also discusses why E<sup>3</sup> protection must be included early into the design of military hardware in order to be affordable, producible, sustainable as well as accommodating to insertions of DMSMS

AEP-41 Volume 1 (Edition 1)

solutions and COTS/NDIs.

**2.2.6 Volume VI.** This volume discusses test and validation. A crucial part of achieving, producing and sustaining UE<sup>3</sup> survivability is a series of E<sup>3</sup> tests that must be performed during all phases of the hardware's life-cycle and tailored to the requirements of the hardware. The basic test types are: engineering development to support the design activities, acceptance (MSCE equipment immunity (both radiated and conducted) and barrier performance (shielding effectiveness and penetration protection devices)), final design validation, production compliance (under Hardness Assurance (HA)), deployment compliance (under Sustainment Assurance (SA)), and Surveillance Test (ST). Both HA and SA includes engineering-type tests and analysis, as necessary, to evaluate and validate that configuration, MSCE, and material changes do not degrade the E<sup>3</sup> survivability level of the hardware by increasing risk to unacceptable levels.

**2.2.7 Volume VII.** This volume discusses hardness and sustainment assurance, and surveillance test. The test and validation aspects of design, engineering development, and hardness assurance are presented in Vol. VI and will be briefly covered in Vol. VII for completeness. Consequently, Vol. VII focuses on sustainment assurance and surveillance test. The objective of a hardness and sustainment assurance program is to establish technical and management activities to ensure that UE<sup>3</sup> survivability achieved and verified during the Engineering Development Phase is not only produced, but, is also preserved throughout the hardware's Deployment Phase or its operational life. Also discussed are methods and guidelines on how to accommodate material changes, technology/DMSMS insertions and associated circuit additions, MSCEs upgrades and modernizations without degrading E<sup>3</sup> survivability to unacceptable risk levels during deployment. Finally, surveillance tests (and analysis) to periodically validate adequacy of both hardness and sustainment assurance programs are discussed.

#### 2.3 Requirements

Military hardware of the six operational categories must be electromagnetically compatible as well as survivable to a myriad of changing EMEs in the battlespace; and, this compatibility and survivability must be readily achievable and affordable as well as producible, maintainable and sustainable throughout the hardware's life-cycle. EMC, survivability, and EME requirements are provided in Section 4 of Volume II.

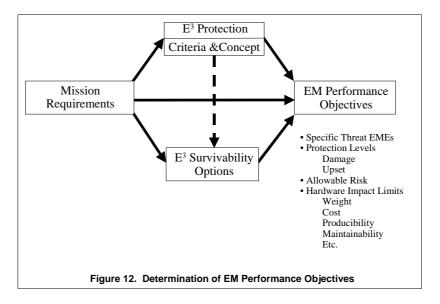

The barrier performance requirements critical to achieving affordable, producible and sustainable UE³ protection for NATO military hardware of the six operational categories are discussed in section 4.0 of Volumes I, III and V. The E³ performance objectives are established from the mission needs, E³ protection criteria and concepts, and the selected E³ survivability options (may require combinations of UE³ barrier protection with alternate and/or special protective methods to achieve survivability). The performance objectives consist of: need to protect against specific EMEs, level of protection required, amount of allowable risk associated with the protection and, as needed, limits on hardware impacts related to E³ protection. See Volume I, Figure 12 for illustration and para.4.2.2 for discussion.

AEP-41 Volume 1 (Edition 1)

objectives be clearly defined early in a program, since they drive performance specifications as well as all subsequent UE<sup>3</sup> protection design and engineering and acceptance test activities, affordability, producibility, sustainability, and flexibility of design.

#### 3.0 AEP 41, VOLUME I, EXECUTIVE SUMMARY

This volume provides the philosophy and details of the methodology for achieving UE<sup>3</sup> protection in the battlespace for all six operational classes of military hardware. The hardening methodology traditionally followed is to consider each EME individually and often serially. The methodology proposed in this AEP is one of unifying EM standards and hardening procedures to simplify EM design and testing, and reduce costs. The basic philosophy is an approach to developing, verifying and implementing balanced UE<sup>3</sup> protection so that E<sup>3</sup> survivability can be achieved that is affordable and can be produced and then maintained and sustained throughout the operational life of military hardware. Balance is achieved between: UE<sup>3</sup> protection design and UE<sup>3</sup> coverage of the EME stresses encountered during operational deployment; unified protection provided, and costs and operational impacts; and level of UE<sup>3</sup> protection and risks of operational degradation. The methodology for implementing this philosophy is performance based, and is dependent on use of an EM barrier protection concept, which uses EM barriers to enclose MSCE unit(s) having inadequate immunity levels, and special protective measures for any MSCE unit(s) requiring additional protection beyond what the barrier provides. Such a barrier typically consists of two essential elements: one or more electromagnetic shields (to include nested shields) and The shield (including mechanical conducted penetrations through the shield(s). penetrations) is called an enclosure port. The conducted penetrations are called penetration ports. Thus, by organizing and controlling the interaction of the EMEs with the hardware, the EM barrier can control the potential impact of these EMEs on the hardware's MSCEs and, ultimately, its mission performance. E<sup>3</sup> survivability is achieved by proper application of the EM barrier combined with alternate methods and special protective measures. A principle advantage of the EM barrier protection concept is that a single barrier can potentially provide the capability for balanced, unified E<sup>3</sup> protection from multiple EMEs. Requirements or allocations for protective features must be tested and validated during engineering development and checked for compliance during production and deployment as shown in Table 2.

Table 2. Typical Life-cycle UE<sup>3</sup> Testing

# AEP-41 Volume 1 (Edition 1)

| TEST TYPE               | OBJECTIVE                                                            | TEST OBJECT                                       | PASS/FAIL CRITERIA                             |

|-------------------------|----------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------|

| ENGINEERING DEVELOPMENT |                                                                      |                                                   |                                                |

| Immunity, EM            | Acquire engineering data to                                          | Bread- and brass-                                 | Data and information                           |

| Emissions,              | support the UE <sup>3</sup> Protection                               | board, MSCE devices                               | does/does-not support UE <sup>3</sup>          |

| Protective              | Design. Establish EM                                                 | and components,                                   | Protection Design                              |

| Devices,                | emission levels, immunity                                            | prototype CCAs,                                   |                                                |

| Shielding               | levels, shielding effectiveness                                      | equipments, and                                   |                                                |

| Effectiveness           | levels, residual levels, and                                         | subsystem, materials,                             |                                                |

|                         | special protective levels.                                           | and port protective devices                       |                                                |

| ACCEPTANCE              | <b>EQUIPMENT IMMUNITY</b>                                            |                                                   |                                                |

| EM Emissions            | Confirm radiated and conducted emissions are within specified limits | Operating assembled MSCEs                         | Lower-bound emissions < allocations            |

| Radiated<br>Immunity    | Confirm radiated MSCEs immunities meet performance objectives        | Operating assembled MSCEs                         | Lower-bound radiated immunities ≥ allocations  |

| Conducted<br>Immunity   | Confirm conducted MSCEs immunities meet performance objectives       | Operating assembled MSCEs                         | Lower-bound conducted immunities ≥ allocations |

| ACCEPTANCE              | BARRIER PERFORMANCE                                                  | =                                                 |                                                |

| Shielding               | Confirm EM shielding                                                 | Electromagnetic shield                            | Measured shielding                             |

| Effectiveness           | effectiveness meet performance requirements                          | with all penetration protective devices installed | effectiveness ≥ performance requirements       |

| Penetration             | Confirm penetration                                                  | Installed conducted                               | Measured residual stresses                     |

| Protection              | protective devices meet                                              | penetration protective                            | ≤ allocations                                  |

| Devices                 | performance requirements                                             | devices in barrier with test loads                |                                                |

| DESIGN VALIDA           | ATION                                                                |                                                   |                                                |

| Illumination            | Confirm production                                                   | Final configuration and                           | Acceptable system operation                    |

| and/or                  | configuration hardware meets                                         | operating hardware                                | and residual stresses ≤                        |

| Injection               | UE <sup>3</sup> survivability requirements                           | , ,                                               | allocations                                    |

| •                       | by threat level EME                                                  |                                                   | Production design is E <sup>3</sup>            |

|                         | illuminations or low- level                                          |                                                   | survivable                                     |

|                         | illuminations plus injections                                        |                                                   |                                                |

|                         | OMPLIANCE - HARDNESS AS                                              |                                                   |                                                |

| Visual                  | Confirm workmanship and                                              | Production hardware                               | Bonds/Grounds ≤ limits. Port                   |

| Inspections             | presence of all port                                                 | Production samples of                             | devices/techniques and                         |

| and                     | devices/techniques and                                               | port penetration                                  | special protective measures                    |

| Measurements            | special protection measures.                                         | devices and special                               | are present and their residual                 |

|                         | Confirm bonds and grounds meet specifications.                       | protective measures.                              | stresses ≤ allocations.                        |

| Illumination            | Confirm production hardware                                          | Production hardware                               | Hardware is E <sup>3</sup> survivable          |

| and/or                  | modified by engineering                                              | and production samples                            | Engineering change residual                    |

| Injection,              | changes can meet existing or                                         | of engineering                                    | stresses ≤ allocations                         |

| Emissions,              | new E <sup>3</sup> survivability criteria.                           | changes.                                          | on occord in an occurrence                     |

| Immunity,               | Confirm engineering changes                                          |                                                   |                                                |

| Protective              | meet performance                                                     |                                                   |                                                |

| Devices,                | requirements.                                                        |                                                   |                                                |

| ,                       |                                                                      | 1                                                 | 1                                              |

AEP-41 Volume 1 (Edition 1)

| Shielding                        |                                                                                          |                                    |                                                                       |  |  |

|----------------------------------|------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------|--|--|

| Effectiveness                    |                                                                                          |                                    |                                                                       |  |  |

|                                  | COMPLIANCE – SUSTAINMENT                                                                 | L ASSURANCE                        | <u> </u>                                                              |  |  |

| Visual                           | Confirm deployed hardware is being properly maintained                                   | Maintained and                     | Hardware is E <sup>3</sup> survivable                                 |  |  |

| Inspections and                  | and repaired, and effects of                                                             | repaired deployed hardware.        | Acceptable system operation and residual stresses ≤                   |  |  |

| Measurements                     | ambient environments, age,<br>and usage has not degraded<br>E <sup>3</sup> survivability |                                    | allocations                                                           |  |  |

| Illuminations,<br>Injections, EM | Confirm deployed hardware modified by engineering                                        | Deployed hardware with engineering | Hardware is E <sup>3</sup> survivable.<br>Engineering change residual |  |  |

| Emissions,                       | changes meets existing or                                                                | changes. Samples of                | stresses ≤ allocations                                                |  |  |

| Immunity,                        | new E <sup>3</sup> survivability criteria.                                               | engineering changes.               |                                                                       |  |  |

| Protective                       | Confirm engineering changes                                                              |                                    |                                                                       |  |  |

| Devices,                         | meet performance                                                                         |                                    |                                                                       |  |  |

| Shielding                        | requirements.,                                                                           |                                    |                                                                       |  |  |

| Effectiveness                    |                                                                                          |                                    |                                                                       |  |  |

| SURVEILLANCE                     | TEST – PRODUCTION                                                                        |                                    |                                                                       |  |  |

| Illuminations,                   | Re-confirm E <sup>3</sup> survivability                                                  | Production Hardware                | Production hardware is E <sup>3</sup>                                 |  |  |

| Injections,                      | and assess adequacy of HA                                                                | and/or selective                   | survivable. Hardware                                                  |  |  |

| shielding                        | Program by performing                                                                    | elements of that                   | elements/items meet                                                   |  |  |

| effectiveness,                   | periodic tests on randomly                                                               | hardware.                          | performance requirements.                                             |  |  |

| Immunity                         | selected production hardware                                                             |                                    | HA Program is/is-not                                                  |  |  |

|                                  | and hardware                                                                             |                                    | adequate.                                                             |  |  |

| 01101/511 1 41105                | elements/items.                                                                          |                                    |                                                                       |  |  |

| SURVEILLANCE TEST – DEPLOYMENT   |                                                                                          |                                    |                                                                       |  |  |

| Illuminations,                   | Re-confirm E <sup>3</sup> survivability                                                  | Maintained as-is                   | Deployed hardware is E <sup>3</sup>                                   |  |  |

| Injections,                      | and assess adequacy of SA                                                                | deployed hardware                  | survivability. Hardware                                               |  |  |

| shielding                        | Program by performing                                                                    |                                    | elements/items meet                                                   |  |  |

| effectiveness,                   | periodic tests on randomly                                                               |                                    | performance requirements.                                             |  |  |

| Immunity                         | selected deployed hardware and hardware elements/items.                                  |                                    | SA Program is/is-not adequate.                                        |  |  |

#### 3.1 Introduction to AEP 41, Volume I

- **3.1.1 Philosophy.** The philosophy is to provide a User-controlled approach to achieving and verifying, and then producing, maintaining and sustaining affordable balanced UE<sup>3</sup> protection and survivability in all six operational categories of NATO military hardware. To be successful, this philosophy must be applied early in the hardware design phase and be made available to design engineers of all levels of assembly in order to be affordable, producible, maintainable and sustainable, and flexible for future upgrades and modernizations. This UE<sup>3</sup> protection philosophy provides a systematic approach for balancing the cost and quality of the EM barrier protection concept against the risk of unacceptable mission degradation and/or failure.

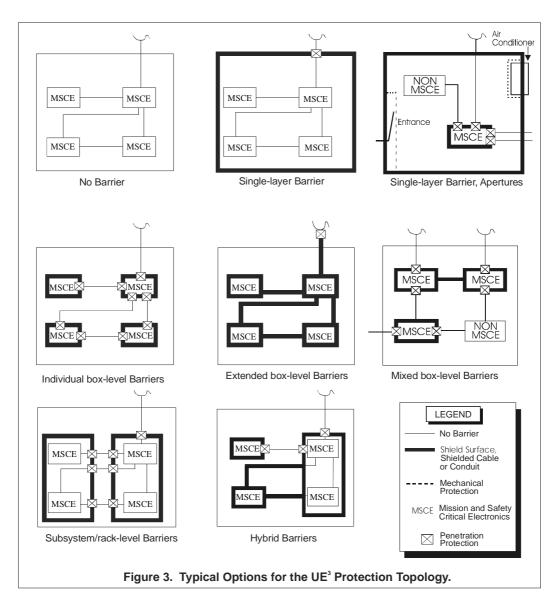

- **3.1.2 Methodology.** The methodology based on use of an EM protection barrier is illustrated in Figures 1 and 2. The actual geometry/topology of the EM barrier can take

AEP-41 Volume 1 (Edition 1)

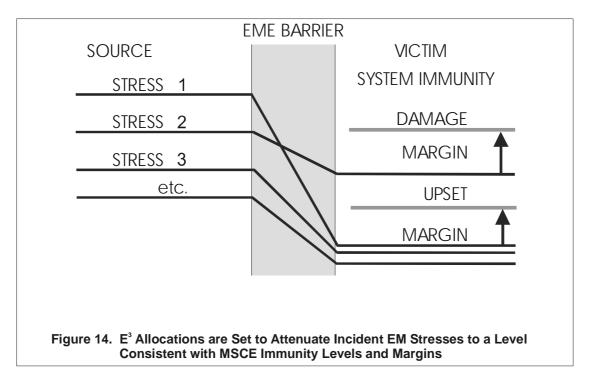

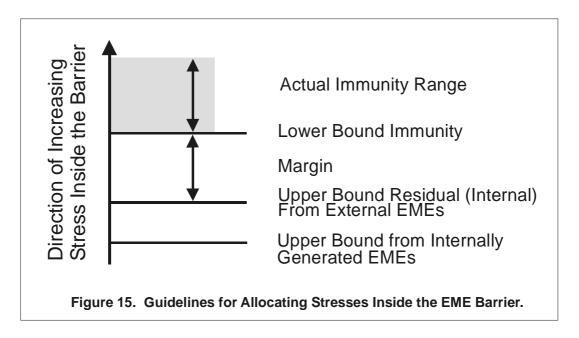

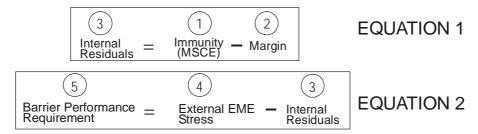

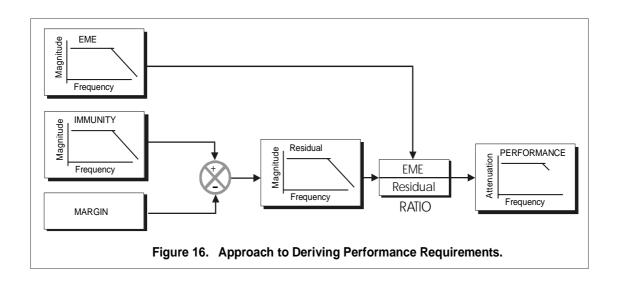

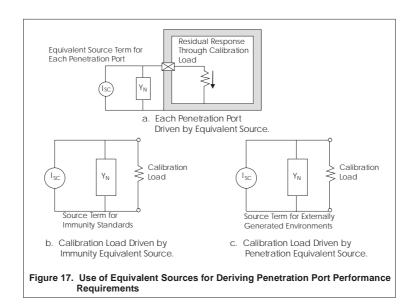

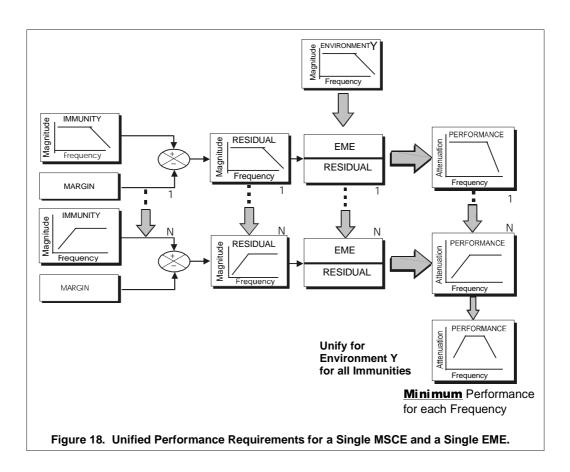

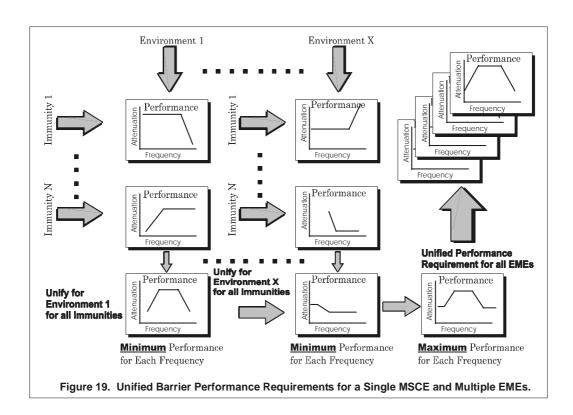

many forms some of which are shown in Figure 3. Note that the options range from no barrier to a complete barrier. Topological decomposition subdivides a problem into a set of volumes (or localized area) through which the EM energy propagates and surfaces through which it penetrates. The purpose of the barrier (where the prime level of unification occurs) is to reduce the externally and internally generated EMEs (conducted and radiated) to residual and stress levels (i.e. voltage and current) consistent with acceptable operation of the protected MSCEs. Shield penetrations (electrical and mechanical) must be controlled through the effective use of penetration protection devices, components and/or mechanical design. Conducted penetration ports are usually controlled with filters for Continuous Wave (CW) EMEs (out-of-band stresses) and nonlinear protection devices for pulsed and multi-pulsed EMEs (in-band stresses). Mechanical penetrations are usually controlled using gaskets, grids, finger stock, and/or Choosing the acceptable operational level and, in turn, the barrier performance requirements, involves a process of balancing the internal residuals from the externally and internally generated EME stresses, the MSCE immunities, and the margin selected to control risk. The engineering trade studies necessary to achieve this balance are called the allocation process, (see Figure 2), which is usually iterative and serves basically as a risk management tool. The allocation approach assigns performance requirements to both the enclosed and penetration ports. The approach can then be used to unify the barrier performance requirements to define a single performance requirement for each port that addresses all applicable immunities and EMEs e.g. single immunity and EME, multiple immunities and single EME, and multiple immunities and EMEs.

## AEP-41 Volume 1 (Edition 1)

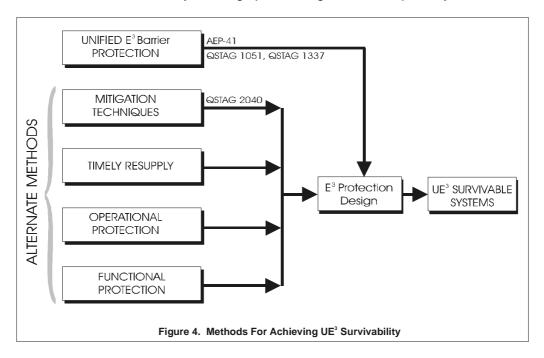

In addition to using the EM barrier, alternate methods such as mitigation, timely re-supply, operational protection, functional protection, etc, should be considered in the design and engineering evaluation process to achieve E³ survivability and for potential cost reduction. Mitigation is often employed in E³ survivability whereas timely supply is not due to the theater-wide HEMP threat. Functional protection can be used along with the EM barrier protection in achieving E³ survivability by addressing upset anomalies through the use of component/software protocols that are fault tolerant and/or circumvention/resets circuits. Operational protection can also assist in achieving E³ survivability by providing the crew procedures to follow when anomalous response occurs. Both operational and functional protections are valuable in surviving upset, thereby, leaving the EM barrier to protect against damage.

AEP-41 Volume 1 (Edition 1)

The proposed methodology simplifies and reduces developmental and verification testing by facilitating unified testing to multiple EMEs to confirm hardware performance, thereby, minimizing test costs and hardware requirements. Table 2 shows typical tests performed during the various acquisition phases.

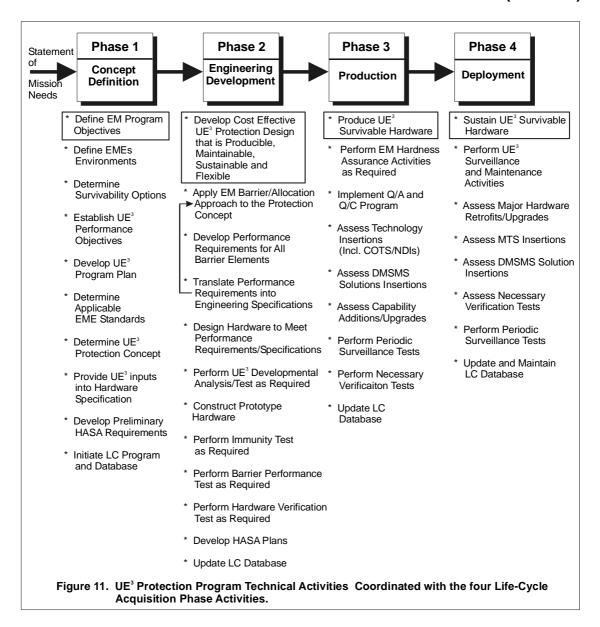

The methodology includes, as an integral part, the designed-in accommodation for HA and SA by focusing on the protective elements [shield(s) and protective devices(s)] and their ability to continue to meets their protection allocations. In addition, this methodology minimizes sensitivity to changes in EME specifications, accommodates reductions in MSCE immunity levels, and simplifies retrofits (if required). Finally, this methodology, by reducing the source generated EMEs to a relatively benign residual EME on the MSCEs, accommodates the incorporation of COTS/NDIs in the design as well as later insertions due to (DMSMS) solutions, technology advances, upgrades and modernization programs such as Modernization-Through-Spares (MTS). Table 3 in Section 4.2 outlines the proposed systematic approach for achieving UE<sup>3</sup> protection.

#### 3.2 Scope for AEP 41, Volume I

#### 3.2.1 Philosophy and Methodology

The scope presents a philosophy and methodology for achieving unified E<sup>3</sup> protection and hardening against battlespace and peace time EMEs such that NATO platforms, systems and equipments will be UE<sup>3</sup> survivable. The methodology employed is based on an EM barrier protection concept whose focus is to ensure that protective features: meets protection allocations in a manner that is cost effective while in concert with other system requirements, can accommodate the use of COTS/NDIs, and, most importantly, can be produced, maintained and sustained throughout the hardware's lifecycle. Various options for achieving adequate and affordable UE<sup>3</sup> protection/hardening will be considered such as: multi-barrier designs and use of nested barriers for victims and sources within the primary EM shield (Figure 1), various barrier topologies (Figure 3), alternate Methods (Figure 4), and special protective methods (Figures 5 and 6). Details will be provided in Para. 4.2.3.4 on how to determine the EM barrier performance requirements for: single EME and single immunity, single EME and multiple immunities, and multiple EMEs and multiple immunities. Unification of the various types of E<sup>3</sup> tests illustrated in Table 2 that must be performed during the last three phases of the hardware's life-cycle are discussed as well as how the tests should be tailored to the operational requirement of the hardware. Finally, a discussion is provided on preserving the integrity of the verified UE<sup>3</sup> protection design and verified level of E<sup>3</sup> survivability during production and deployment. Included are discussions on potential impacts due to: insertions and/or additions of more energy sensitive MSCEs. addition of new MSCEs and equipments to enhance capabilities, and debilitating effects from age, corrosion, usage, imperfect maintenance, and repeated exposure to EM and ambient environments.

#### 3.2.2 Risks

AEP-41 Volume 1 (Edition 1)

There are risks with an E<sup>3</sup> protection concept, as well as the implementation, production, and sustainment of that concept during the life-cycle. These risks are driven primarily by: funding and time limitations, inadequate EM protection design, late insertion and development of the UE<sup>3</sup> protection design, no implementation of a well thought-out HA/SA program, and inadequate testing. Consequently, there is risk in all four life-cycle phases. To minimize and manage risks, a hardening approach must be developed during the design concept phase, implemented and validated during the engineering phase, and preserved during the production and deployment phase. Therefore, a thorough life-cycle program must be defined and implemented during the concept/design phase and fully developed during the engineering development phase. The life-cycle program, HA and SA, will manage and preserve the E<sup>3</sup> survivability design. The database of the life-cycle program must be updated with pertinent data, results, and information throughout the remainder of the acquisition phases. The lifecycle program itself will experience changes due to corrective action for inadequacies, improvements due to new knowledge, and updates for engineering, modernization, EME, and other changes. Thus, the implementation of early-in-design E<sup>3</sup> survivability based on the UE<sup>3</sup> protection concept followed by a well designed HA and SA program is the best tool for risk management.

# 4.0 UNIFIED ELECTROMAGNETIC ENVIRONMENTAL EFFECTS PROTECTION

#### 4.1 Overview

#### 4.1.1 General

Presented is an affordable approach to achieve UE³ protection, based upon the EM barrier protection concept, that is practical; yet, achieves E³ survivability in the battlespace for all classes of NATO platforms, systems and equipments of the six operational categories. Adequate E³ protection of electronic/electrical material is essential since these military hardware must operate during and after exposure to increasingly severe, complex and changing EMEs that can potentially impact crew safety as well as degrade or destroy mission essential capabilities. In addition, the hardware must remain E³ survivable for much longer periods of deployment (>50 years for many) while accommodating multiple upgrades and modernizations. The hardware must remain survivable against the traditional degradation impacts from ambient environments, aging, usage, and repeated maintenance and repairs. Today's hardware must also remain survivable against new factors such as integration of COTS/NDIs, and DMS-solution and technology insertions. (See AEP-50 and Vol. II of this AEP)

#### 4.1.2 Electromagnetic Environments (EMEs)

Three general types of EMEs that military hardware must be survivable to are discussed in detail in Volume II and briefly below:

AEP-41 Volume 1 (Edition 1)

Naturally Occurring EMEs: Electrostatic discharge (ESD) and lightning are the two types of naturally occurring EMEs specified for most military hardware. Precipitation static (P-Static) applies primarily to OC5 platforms and briefly to the launch phase of OC3 systems. ESD by personnel applies to MSCEs of all six OCs of military hardware due to personnel involvement. ESD by helicopter applies to OC1, OC4, OC5 and OC6 due to landing of vertical lift aircraft, inflight refueling, and systems operated or transported externally by vertical lift aircraft. Both NSL and DSL environments can affect all six OCs of military equipment. Except for regions of the poles, lightning is prevalent over all portions of the earth.

**Electronics Operation Generated EMEs:** Whenever electrical or electronic circuits operate, EM fields and/or currents are produced. These EM fields and currents can, in turn, affect or interfere with operational performance of victim MSCEs by a process called EM Interference (EMI). The EMEs due to electronic operation can be generated outside and/or inside the victim's hardware (See Table 1). The EMEs generated outside the victim's hardware are due to the operation of neighboring or remotely located hardware, or even remote or external units of the victim's hardware. Included in this category of externally generated EMEs is High Intensity Radiated Field (HIRF) generated by radars or other high-power emitters. When military hardware operates sufficiently close to HIRF emitters, the victim's electronic circuits and operations can be affected. Survivability to these external EMEs is normally addressed under control of EMI characteristics for equipments or inter-system EM Compatibility (EMC) for systems and platforms. Harmful levels of EMEs can also be generated internal to the hardware by the operation of electrical or electronic circuits within the hardware. These EME sources can cause neighboring electronic MSCE units or hardware to functionally upset or to be damaged. Survivability to these internal EMEs is normally addressed under control of EMI characteristics of equipments or intra-system EMC for systems and platforms.

#### **Hostile EMEs:**

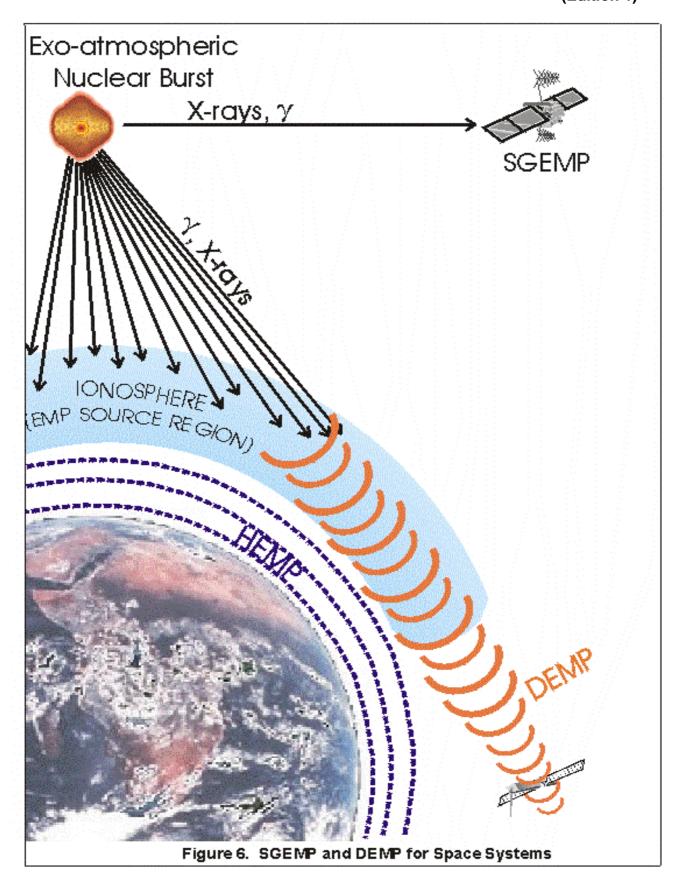

Hostile EMEs are generated by an adversary for the specific purpose of degrading the performance of the victim's MSCEs. Hostile EMEs considered in this AEP are of two types: nuclear and non-nuclear generated. Nuclear weapon generated EME includes: High-Altitude Electromagnetic Pulse (HEMP), System Generated EMP (SGEMP), and Dispersed EMP (DEMP) for exo-atmospheric burst; and Source-Region EMP (SREMP) for endo-The HEMP has early, intermediate, and late time atmospheric burst. components. However, for most terrestrial hardware only the early time HEMP component requirement is considered. SGEMP results from the weapon's prompt gammas interacting directly with a system (OC-1, OC-2 and OC-6), and prompt gammas and X-rays interacting directly with a system's surface (OC3). In particular, the two internal components of SGEMP (box internal EMP (IEMP) and cable IEMP) are of great concern to space systems (AEP-50). DEMP is an unique case of HEMP where the radiated signal misses the earth and propagates through the ionosphere to a distant line-of-sight satellite (OC3

AEP-41 Volume 1 (Edition 1)

system, AEP-50). Although DEMP<SGEMP in magnitude, DEMP should be considered for satellite hardening because its frequency spectrum and pulse (similar to a swept CW waveform) may be considerably different than those of a SGEMP. This is due to the HEMP that traverses the ionosphere (a dispersive medium) to the satellite is "stretched out". SREMP formerly called low-altitude EMP (AEP-4) is a complex environment consisting of a deposition region of high air conductivity (both electronic and ionic) that decreases away from the burst point, and a localized EMP (sometimes referred to as endo-atmospheric EMP) with considerable horizontal magnetic and vertical electric field components. In addition, SREMP has a gamma pulse component that can directly interact with a system releasing Compton electrons, which, in turn, produces a complex EME that includes external and internal fields and currents induced on surfaces and within cables. Since hardware or hardware elements must be within the deposition region to be at risk, SREMP is normally considered for certain OC1 systems (AEP-20), OC2 systems (SHAPE 1460-3), and OC6 systems (AEP-19 and -20).

Non-nuclear weapon generated hostile EME includes High-Power Microwave (HPM), Non-Nuclear EMP (N²EMP), and Ultra-Wideband (UWB). High power emitters consisting of RF generators, pulse forming networks, and directional antennas typically produce these hostile EMEs In addition, there are other types of hostile EMEs that will not be considered in this AEP such as Electronic Warfare and laser.

Any of these EMEs may interrupt, obstruct, or otherwise degrade or limit the effective performance of MSCEs or electrical equipment. As such, any of these EMEs may cause EMI that results in EM Compatibility (EMC) problems within the system or platform, or at the system or platform level [ANSI C63.14-1992]. Partial or complete loss of mission capability may result from these EMEs. A list of the EMEs is shown in Table 1.

#### 4.1.3 Electromagnetic Environmental Effects (E<sup>3</sup>) Survivability

**4.1.3.1 UE**<sup>3</sup> **Protection.** In general, the military hardware performance degradations are due to either functional upset or permanent damage of MSCEs caused by EME induced stresses. The purpose of the EM protection barrier is to provide a tool for control of the EMEs so that their resulting residuals are levels that enable the hardware's operational requirements to be met; and, furthermore, UE<sup>3</sup> survivability achieved to be preserved throughout production and deployment. The actual EM barrier geometry can take many forms some of which are illustrated in Figure 3. Note that these topology options range from: no barrier, assuming the allocation burden is placed entirely upon the MSCE's immunities; to a single-layer integral barrier where the allocation burden is placed entirely on the barrier; to subsystem/rack level barriers that can be tailored for controlling EME stresses in different regions of the hardware; to box level barriers that protect the individual MSCE units; to hybrid barriers that utilize the EME stress control features of both subsystem/rack and box level barriers.

AEP-41 Volume 1 (Edition 1)

#### 4.1.3.2 Alternate and Special Protective Methods.

- **4.1.3.2.1 Alternate Methods**. In combination with the UE<sup>3</sup> barrier, alternative methods may be desired in achieving E<sup>3</sup> survivability and reducing cost. Evaluation and selection of methods to be combined with the UE<sup>3</sup> barrier must occur in the design phase in order to be cost and design effective. The concept of using combination of methods to achieve E<sup>3</sup> survivability is shown in Figure 4.

- **4.1.3.2.2 Special Protective Methods**. There are cases where special protective measures are required because adequate UE<sup>3</sup> protection cannot be achieved with the EM barrier alone. All volumes discuss these cases as they pertain to the volume's subject. Three major cases are provided.

- a. The first case involves additional shielding, equipment-level protection, and/or unique penetration protection devices to achieve adequate E³ survivability. Typical cases involve MSCEs that are: outside the EM barrier, within the EM barrier but still experience unacceptable responses (measured during subsequent verification testing), or within the EM barrier but still need additional supplementary isolation due to regular protection device interference with hardware's operation. Special protection measures should only be used for exceptional cases and not as a substitute for the EM barrier if all performance requirements can be met by the barrier.

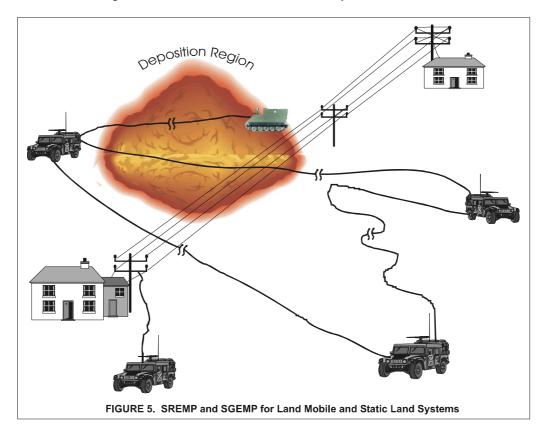

- b. A second case involves SREMP, which can affect hardware that are within or have conductive elements within the deposition or source region of a surface or nearsurface endo-atmospheric nuclear event. As illustrated in Figure 5, SREMP occurs when the armored protected system (OC1) is within the deposition region and survives the other nuclear environments such as airblast, thermal radiation and initial nuclear radiation. Strong peak vertical electric fields (10s of kV/m) and horizontal magnetic fields (100s of A/m) are generated and can interact with the armored system producing currents and voltages on cables. These electric and magnetic fields are not perpendicular to one another in the traditional way due to the air conductivity being alter by interactions of Compton electrons (initially released from the gamma photon interaction with air molecules) with air molecules producing secondary electrons. In turn, these secondary electrons cause the air to become conductive producing effects in addition to the EMP-type EMEs. Both the environments and effects on hardware are difficult to predict. SREMP also has a large-in-magnitude peak gamma dose component in the deposition region that can interact with the conductive materials of armored systems or static hardened systems producing external SGEMP as well as internal SGEMP (box IEMP and cable IEMP). Thus, an armored command and control vehicle (OC1) can be affected by the SREMP generated SGEMP as well as the burst generated EMP. Illustrated in Figure 5 is a non-armored sheltered-based mobile command and control (C<sup>2</sup>) unit (OC6) consisting of the C<sup>2</sup> systems outside the deposition region but are interconnected with long signal cables that go through the deposition region. The C<sup>2</sup> systems are unaffected directly but are affected indirectly due to induced currents and voltages into the interconnecting cables. Also shown in Figure 5 is another hypothetical case of commercial power transmission lines passing through the outer portion of the deposition region. These conductive lines connect to one of the mobile C<sup>2</sup>

AEP-41 Volume 1 (Edition 1)

systems located outside deposition region as well as a  $\mbox{C}^2$  static site (OC2) causing upset or even damage to end-item MSCEs in both OC systems.

A third case requiring special protective methods, shown in Figure 6, is a scenario of an exo-atmospheric nuclear detonation affecting line-of-sight satellites. A nuclear detonation produces copious quantities of gammas and x- rays. These photons become the source of SGEMP for near line-of-sight satellites (OC3) as well as the EMP source region in the ionosphere that produces HEMP for terrestrial hardware (all OCs) and DEMP for a special cased of a distant line-of-sight satellite. The incident gammas and X-rays interact directly with the satellites' surface releasing Compton and photoelectric electrons that produces external and internal currents. External SGEMP can affect external equipments and enter into the interior via port-of-entries (POE). Diffusion through the satellites' skin can be usually be ignored because it is a lesser effect than those from POE penetrations or internal SGEMP. The penetrating energetic photons will create free electrons inside the satellite, which becomes the source of electric and magnetic fields. These fields become the source for two internal SGEMP components, internal fields or box IEMP and cable currents or cable IEMP. Of the three types of SGEMPs, typically the cable IEMP produces the largest internal open-circuit voltages and short-circuit currents. Although DEMP (~10 V/m) is usually not a problem if the satellite is hardened to survive SGEMP (box IEMP, ~100s V/m); DEMP should still be considered in the design because it has different coupling characteristics than SGEMP due to the EMP being stretched out as it traverses the ionosphere to the satellite. If no SGEMP hardening has been provided, then even the small DEMP environment can be a threat by causing spurious signals in the space system.

AEP-41 Volume 1 (Edition 1)

#### 4.1.4 Evolution of Electronics and COTS/NDI Usage

To achieve UE<sup>3</sup> survivability, adequate protection of all MSCEs must occur against both externally and internally generated EMEs. The MSCEs requiring protection are becoming increasingly more sophisticated, complex and sensitive to EMI. The increase in EMI sensitivities are due to: higher operating frequencies of digital electronics, smaller feature sizes, greater use of energy sensitive technologies, continued evolution to lower operating voltages for circuits and devices, increasing use of plastic encapsulated microcircuits (less inherent shielding), higher integration densities (both within packages and circuits), and increase use of COTS/NDIs. Consequently, the increasing use of these sophisticated electronics in the design, production, and, especially, in the deployment (maintenance/repairs/upgrades) of military hardware emphasizes the importance of applying an encompassing, versatile UE<sup>3</sup> protection scheme employing the EM barrier protection concept. It is especially important that this protection concept be incorporated early into hardware design in order to be affordable, achievable, and versatile to accommodate the many future changes involving MSCEs most of which will have lower immunity levels. In addition, this UE<sup>3</sup> protection scheme must be one that allows for COTS/NDIs to be used at all assembly levels in the initial design and the design as it matures as well as the design during production and deployment. Integration of COTS/NDI into the hardware throughout its life-cycle must be planned because such integration will occur to accommodate DMSMS solution and technology insertions, changes due to upgrades and modernizations, and changes due to maintenance and repair.—As an example, the MTS Program is a performance based concept that integrates state-of-the-art electronics into aging systems as part of maintenance for the explicit purpose to stabilize Mean Time Between Failure Rates (MTBFRs), improve readiness levels, increase the hardware's battlespace performance capabilities, and be proactive in regards to DMSMS issues.

#### 4.1.5 Unified E<sup>3</sup> Protection Approach Overview

#### 4.1.5.1 General

This section presents and overview of the procedures for achieving balanced E<sup>3</sup> hardening. Details follow in the paragraph 4.2

When applying the Unified Approach to E³ protection, it might be possible to combine time or frequency EMEs together to reduce design, analysis and/or test costs. However, there are significant technical issues that must be considered. These are discussed in detail in Volume III.

#### 4.1.5.2 Route to Adequate Protection

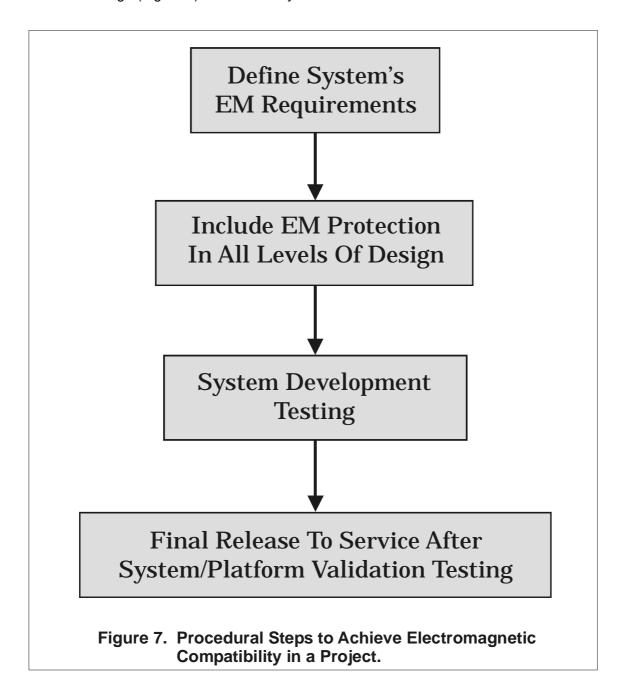

**4.1.5.2.1 Development of E<sup>3</sup> Protection:** Figure 7 is a flowchart showing the basic procedural steps to be followed in achieving EMC in a project. These steps occur during a hardware design concept and engineering development program (Phases 1 and 2).

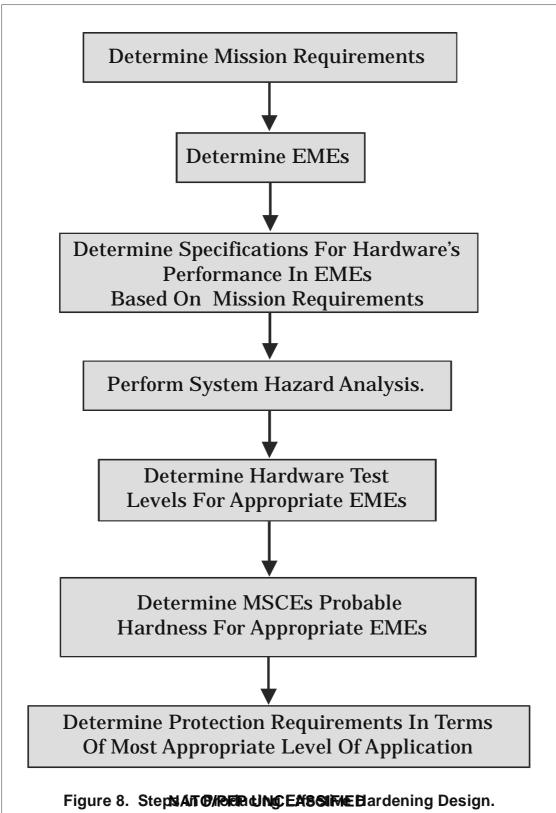

# **4.1.5.2.2 Hardening Requirements:** Figure 8 shows the steps in developing NATO/PFP UNCLASSIFIED

AEP-41 Volume 1 (Edition 1)

effective hardening requirements in a program to ensure suitable in-built protection in the final hardware. These seven steps are the hardening activities required to achieve an EMC design (Figure 7) and are briefly discussed.

AEP-41 Volume 1 (Edition 1)

#### **Step 1: Determine Mission Requirement**

The mission requirements of the hardware are determined, and the various scenarios to be used is defined. These factors govern the EMEs that the hardware is likely to encounter during its entire deployment lifetime. For instance, the requirements on transport hardware may be very much lower then those for a front line combat hardware, although multi-role hardware will have to be designed to cover the worst case EME they may encounter.

#### **Step 2: Determine EMEs**

The various EMEs are defined in detail in Volume II of this AEP and listed in Table 1. All EME threats are continuously updated due to a better understanding of the EME threat as in the case of lightning, new EME transmitters coming on-line, new threat scenarios, or insertion of more E<sup>3</sup> sensitive MSCE devices or units. EME threat projections are critical in defining the built-in design features, design flexibility, and margins.

The "my threat is larger than your threat" syndrome that tends to be prevalent when various groups are competing for funds must not be allowed to color the judgment of the program manager. All EME threats should initially be given equal consideration in a procurement program. An EME threat, which may be worst case for one system, may not be for another, and changes in constructional material can impact on which EME threat can cause the biggest problems. For instance, the use of carbon fiber composite in airframes increases the lightning protection required due to the composite's poorer electrical and thermal conductivity properties.

#### **Step 3: Determine Hardware Specification**

It is important to tailor the requirements to those needed to ensure that the required hardware performance is met. Sometimes, equipments may be used on several platforms/systems; therefore, platform/system specifications applied to such equipments must be encompassing.

Over-specifying will involve cost penalties. A degree of degradation may be permissible. It may not be necessary for all the equipment to work all the time. An example of this may be lightning strike where on some aircraft programs, only flight critical equipments are protected, not mission critical equipment, as the probability of a strike is low and the resultant attrition would be acceptable. Another example involves many ground and naval systems/platforms when operational recovery can occur within a specified timeframe due to crew intervention (without hardware replacement or repairs); thus, preventing the need for hardening to a more expensive and difficult requirement of operate-through.

Under specifying may mean the platform/system fails to meet its mission requirements in all areas of the EME battlespace. In addition, the platform/system will unlikely be able to accommodate future electronic insertions or EME threat changes without

AEP-41 Volume 1 (Edition 1)

expensive re-designs to achieve adequate hardening. Also, one would anticipate later increase in susceptibilities due to normal E<sup>3</sup> protection degradation that occurs during deployment.

# Step 4: Perform System Hazard Analysis: i.e. Determine Hardware Criticality and Upset Criteria

The functional criticality of the various hardware equipments must be defined. This will define the severity of the requirements to be put on the supplier of the hardware. The performance requirements of the hardware can then be defined in terms of allowable upset. An example of this is in the civil aircraft environment where there is an "everyday" and a Level I "emergency" environment with different performance requirements for the systems. Another example may be armored or mobile missile systems where upsets are allowed so long as crew intervention can restore system functionality within a specified period, say 5 minutes, and without changing components.

# **Step 5: Determine Hardware Test Levels**

Now that the EME and required performance has been defined, the test specifications complete with levels can be defined. This can be assisted by the use of data from previous hardware tests such as the transfer functions defining the relationship between the external threat fields and the stresses at the internal MSCEs. These will provide a reasonable assessment of the internal environment the systems designer must protect against and provide test levels for the military hardware compliance specifications/standards. It must be remembered that the limits provided in military EMI/EMC standards such as AECTP 500 series are for guidance and need to be tailored for particular applications.

Where possible, the defined internal environments and test procedures can be integrated together to reduce test costs and aid in the design stages.

# **Step 6: Determine MSCEs Probable Hardness**

In today's environment, usage and later insertions of COTS/NDIs must be planned and designed for. As no or minimal control can be applied to their individual E³ hardness, an assessment of their E³ hardness or immunity levels will aid in defining extra design measures which need to be taken to protect these COTS/NDIs when installed, and prevent possible compromise of the hardware performance. However, the EM barrier protection concept to include good margins and planned flexibility in the design will enable future COTS/NDIs insertions and additions to occur without major impacts such as major re-designs and/or hardening efforts/costs. A discussion on COTS/NDIs vulnerabilities can be found in Volume IV "Susceptibility of Platforms, Systems and Equipments to E³"

# **Step 7: Determine Protection Requirements**

AEP-41 Volume 1 (Edition 1)

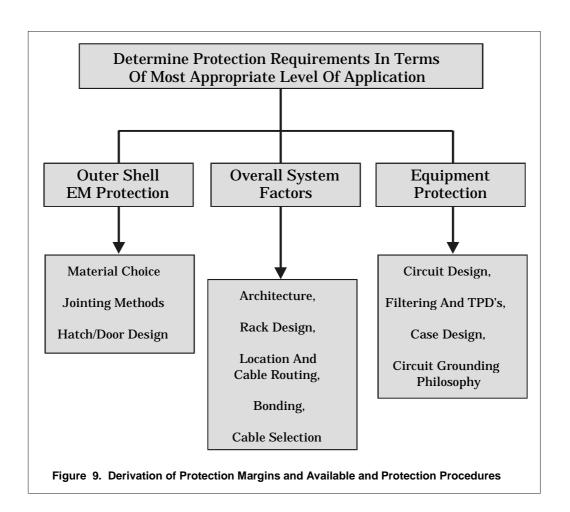

The required protection of the hardware is usually defined in terms of various required performance characteristics of the various "barriers". These performance characteristics are dependent on the EME threat and the type of "barrier" being specified. EME threat unification can ease the definition of the requirements but extreme care is required when attempting to unify the requirements for time and frequency domain threats. Often, only partial unification of protection requirements is practical. Figure 9 illustrates examples of the various protection methods available to the designer. Some of the protection procedures revolve around the use of protective devices such as metal oxide varistors (MOVs), transorbs, surge arrestors, filters or system skin design. Others revolve around more esoteric methods, such as system and software architecture. The latter group is harder to characterize in terms of protection requirements. Protection methodology is discussed in detail in Volume V: "Unified Hardening and Protection Against E<sup>3</sup>".

**4.1.5.2.3 Testing and Validation of UE³ Protection** The final two stages of Figure 7 are tests and evaluations, which are essential and must be performed in order to ensure adequacy and that the protection design meets hardware specifications and compliance requirements. Testing is both a critical and an integral part of the UE³ protection concept. Tests are designed to aid in the allocation process by determining MSCE unit immunity levels and the determination of the ability of the protection features to meet their protection allocations rather than simulating individual EMEs. These tests aid in developing the detailed design (Phase 1), demonstrating final compliance (Phase 2), and demonstrating adequate E³ protection is entering production (Phase 3). Commercial test standard should be used when appropriate. First principle analyses are often used in the allocation process. Table 2 provides a summary of the E³ test protocol guidelines for testing during a system's life-cycle. The test methods are discussed in detail in Volume VI: "Testing and Validation of E³ Protection"